ЫцзХШЫУЧЖдгкЭЈбЖЭјТЗвдМАЕЕАИДЋЪфЕФашЧѓгыШеОудіЃЌИпаЇФмЭЈбЖЯЕЭГйВШЛвбГЩЮЊЯжНёзюЮЊживЊЕФЗЂеЙвщЬтЁЃЕЋвђЭЈбЖДЋЪфЫйТЪДѓЗљЬсЩ§ЃЌЪБТіЖЖЖЏЃЈjitterЃЉЖдгкЯЕЭГНЋЛсдьГЩбЯжиЕФгАЯьЃЌЫљвдВЛЙмШЮКЮЯрЙиВњЦЗНдБиашЭЈЙ§ЖЖЖЏСПбщжЄКѓВХПЩНјШыСПВњЁЃгаМјгкДЫЃЌдкБОЮФжаНЋЬсГівЛФкНЈЖЖЖЏВтЪдМмЙЙЃЌвВОЭЪЧВЩгУЖЖЖЏЗХДѓдРэДюХфТіВЈЭЬЪЩЃЈPulse RemoveЃЛPRЃЉжЎММЪѕЃЌЪЕЯжГіИќзМШЗМАИќгааЇТЪЕФФкНЈЖЖЖЏВтЪдЕчТЗЃЌвдМѕЩйЭтВПвЧЦїжЎашЧѓНјЖјДѓЗљНЕЕЭЩњВњВтЪдГЩБОЁЃ

ЧАбд

ЪБађЖЖЖЏЃЈtiming jitterЃЉЮЊЯЕЭГЩшМЦжаЦеБщДцдкЕФЮЪЬтЁЃЕЋЪЧвђЮЊдчЦкЯЕЭГЪЙгУашЧѓСПВЛИпЃЌЫљвдНдЭИЙ§НЯЕЭЕФбЖКХДЋЪфЫйЖШМѕЩйЩшМЦИКЕЃЃЌвВвђДЫЖЖЖЏЯрНЯгкећИіжмЦкЪБМфЫљеМЕФБШР§ЗЧГЃЮЂаЁЁЃЫцзХЛ§ЬхЕчТЗШеаТдТвьЃЌШЫУЧЦеМАЪЙгУЕчФдВЂдіМгЭЈбЖЦЕПэашЧѓЃЌдкИїжжЭЈбЖаЖЈЩЯЖМДѓЗљдіМгЦфВйзїЫйЖШЁЃдкЯрЭЌЬѕМўЯТЪБађЖЖЖЏвбдкбЖКХМфеМгаЯрЕБДѓЕФАйЗжБШЁЃвђДЫгыЪБТіЯрЙиЕФЯЕЭГЖМЛсеыЖдЖЖЖЏзіНјвЛВНЕФЙцЗЖЁЃ

ФПЧАЖЖЖЏСПнЭШЁЕФЗНЪННдНхгЩвЧЦїЭтВПСПВтЫљЕУЃЌЕЋЕБЯЕЭГВйзїЫйТЪдіМгКѓгкСПВтЩЯЛсгіЕНвдЯТСНИіЮЪЬтЃКВтЪдГЩБОЃЈcostЃЉгыВтЪдзМШЗЖШЃЈaccuracyЃЉЁЃДгВтЪдГЩБОЙлЕуРДПДЃЌШєвЊСПВтGHzвдЩЯбЖКХЃЌЪОВЈЦїЮЊЕУЕНзМШЗСПВтЪ§жЕЦфШЁбљТЪБиаыЗЧГЃИпЫйЃЌЖЏщќЪ§ЪЎGS/sЁЃвђДЫШэгВЬхЪЕЯжБфЕУЗЧГЃРЇФбЃЌВтЪдЛњЬЈГЩБОвВОЭДѓЗљЬсЩ§ЁЃДЫЭтЃЌВЩгУЭтВПвЧЦїВтЪдОЇЦЌФкВПбЖКХЃЌвВЛсВњЩњСПВтПЩППЖШЕФЮЪЬтЁЃР§ШчВтЪдЛЗОГЖдгкД§ВтбЖКХЕФИЩШХЁЂI/OНщУцЦЕПэжЎЯожЦЁЂОЇЦЌФкВПЪфГіЛКГхЦїЃЈoutput bufferЃЉЕФдгбЖ…ЕШЕШЃЌетаЉНдЛсдьГЩСПВтЪ§жЕзМШЗЖШЯТНЕЁЃ

ЮЊНтОіЯрЙиВтЪдЮЪЬтЃЌФПЧАБИЪмжѕФПЕФЗНЗЈОЭЪЧМгШыПЩВтЪдадЩшМЦЃЈDesign for TestabilityЃЛDfTЃЉЁЃПЩВтЪдадЩшМЦЕФЙлФюЪЧдкЩшМЦСїГЬжаМгШыСПВтЕФПМСПЃЌЛђЪЧНхгЩвЛаЉЖюЭтИЈжњдЫЫуЗНЪНРДНЕЕЭЖдздЖЏВтЪдЩшБИадФмЕФвЊЧѓЁЂМАДѓЗљНЕЕЭЩњВњВтЪдЫљашжЎГЩБОгыЪБМфЁЃШЛЖјДЫВтЪдЗНЪНЫфПЩМѕЩйВтЪдГЩБОКЭЪБМфЃЌЕЋзюБЛЪаГЁЫљкИВЁЕФЪЧЦфзМШЗадЁЃетЪЧвђЮЊЖюЭтЕчТЗНЋЛсзЂШыдгбЖгкД§ВтЕчТЗжаЃЌЧввВЮоЗЈШЗБЃДЫЕчТЗЩшМЦЪЧЗёЭъЩЦЃЛДЫЭтРћгУЖюЭтЕФдЫЫуЗНЪНБиаыЯШШЗБЃД§ВтЪ§жЕЛђЪЧД§ВтЛЗОГЩшЖЈЮоЮѓЃЌЗёдђОЭЫуДѓЗљЫѕЖЬВтЪдЪБМфвВЪЧЭНРЭЮоЙІЁЃ

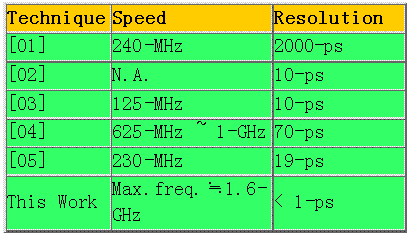

БОЮФНЋЬсГівЛПЩФкНЈгкОЇЦЌжаСПВтЪБТіЖЖЖЏСПжЎВтЪдЯыЗЈгыМмЙЙЁЃЦфВЩгУЕЅпЂШЁЃЈsingle-shotЃЉСПВтЗНЪНДюХфЪБМфЗХДѓЕФММЧЩНЋбЖКХЖЖЖЏСПЕШБЖТЪдіМгЃЌРДМѕЧсЪБМфЪ§ЮЛзЊЛЛЕчТЗЃЈTime-to-Digital ConverterЃЛTDCЃЉдкжЦГЬЩЯЕФЯожЦЁЂНјЖјЬсЩ§ВтЪдНтЮіЖШЃЈresolutionЃЉЁЃДЫЭтДюХфЪЙгУТіВЈЭЬЪЩжЎЕчТЗММЪѕЃЌЪЙЕУМмЙЙОпгаМЋМбЯпадЖШЁЃЯрНЯгыДЋЭГФкНЈЖЖЖЏСПВтЕчТЗЃЈ[1]~[5]ЃЉЃЌЦфОпБИПэЦЕВйзївдМАЕЭЖЖЖЏСПВтЪджЎЬиадЃЌВЂгаНЯаЁЕФГЌЖюУцЛ§ТЪЃЈarea overheadЃЉЁЃ

Background

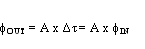

ЗЂеЙжСНёЃЌФкНЈЪБТіЖЖЖЏВтЪдММЪѕгаМИжжНЯЮЊЦеБщЕФВтЪдМмЙЙЃЌгааЉвбгІгУгквЕНчВњЦЗВтЪджаЃЌЯШеыЖдетаЉДЋЭГМмЙЙзіНјвЛВННщЩмЁЃ

Delay Chain [1]

ЁЖЭМвЛЁЁЪЙгУdelay chainжЎЖЖЖЏСПВтЗЈЁЗ

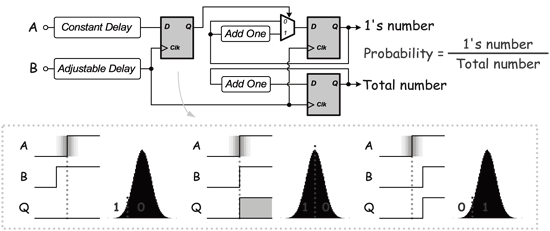

ДЫВтЪдМмЙЙЮЊLogic Visionгк1999ФъЬсГіЃЌЪЧРћгУПЩЕїећбгГйЯпЃЈAdjustable Delay LineЃЛADLЃЉЁЂе§ЗДЦїгыМЦЪ§ЦїДюХфЭГМЦдРэРДВтЪдЖЖЖЏСПЁЃе§ЗДЦїОЭКУБШЪЧвЛИіЯрЮЛМьВтЦїЃЌШєЕїећбгГйСПЪЙЕУBСьЧАAЃЌДЫЪБ0ГіЯжЕФЛњТЪНЋеМЖрЪ§ЃЛЗДжЎЕБBТфКѓгкAЃЌдђ1ГіЯжЕФЛњТЪНЋеМЖрЪ§ЁЃврМДНхгЩЕїећВЛЭЌбгГйСПРДЕУЕНВЛЭЌЛњТЪЗжВМЃЌдйДюХфЩЯРлЛ§ЗжВМКЏЪ§ЕФдЫЫуЃЈCumulative Distribution FunctionЃЛCDFЃЉНЋЖЖЖЏСПдЫЫуГіРДЁЃ

гХЕуЃК

ЁёМмЙЙМђЕЅЧвШнвзЪЕЯжЁЃ

ШБЕуЃК

ЁёбгГйЯпЛсгаЦЕТЪЕФЯожЦЃЌДЫНЋгАЯьВйзїЗЖЮЇЁЃ

ЁёашЕїећбгГйЪБМфРДЕУЕН1ЁЂ0ЗжВМНјЖјЕУжЊЖЖЖЏСПЃЌвђДЫНЋашШпГЄЕФВтЪдЪБМфЁЃ

Two Ring Oscillators [2]

ЁЖЭМЖў ЪЙгУtwo ring oscillatorsжЎЖЖЖЏСПВтЗЈЁЗ

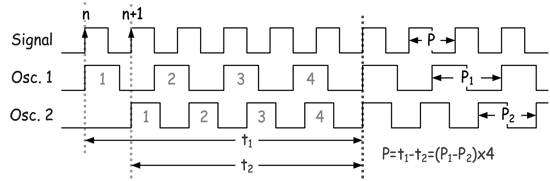

ДЫВтЪдМмЙЙдђЮЊCredenceгк1999ФъЫљЬсГіЃЌЪЧЪЙгУСНзщвбжЊЕЋВЛЭЌВйзїЦЕТЪЕФФкНЈеёЕДЦїЃЌРћгУД§ВтЪБТібЖКХЕФЕкnИігыЕкn+1ИіжмЦкЗжБ№ШЅДЅЗЂеёЕДЦїЪЙЦфПЊЪМеёЕДЁЃЕБСНепВЛЭЌжмЦкЪБТіжЎЯрЮЛЮЧКЯКѓЃЌдйРћгУЯрЮЛЮЧКЯЫљашЕФжмЦкЪ§ДюХфеёЕДжмЦкМДПЩЗДЭЦЪБТіЖЖЖЏСПЁЃ

гХЕуЃК

ЁёВЩгУДЅЗЂеёЕДЕФЗНЪНЃЌбЖКХВЛЛсвђЮЊОЙ§delay chainКѓduty cycleЖјЪмЕНгАЯьЃЌЯрНЯгкЧАУцЕФзїЗЈОпгаНЯЙуЕФСПВтЗЖЮЇЁЃ

ШБЕуЃК

ЁёЖЖЖЏСПЪЧОЖрИіжмЦкБШНЯКѓЫљЕУЃЌвђДЫВтЪдЪБМфНЋЪЧзюДѓЕФПМСПЁЃ

ЁёЪЙгУСНзщеёЕДЦїжЎЯрЮЛБШНЯРДЕУЕНЖЖЖЏСПЃЌШєеёЕДЦЕТЪЦЏвЦНЋдьГЩВтЪдЮѓВюЁЃ

ЁёашЖюЭтЕФЭГМЦЕчТЗИЈжњЃЌГЩБОНЯИпЁЃ

Vernier Delay Line [3]

ЁЖЭМШ§ ЪЙгУvernier delay lineжЎЖЖЖЏСПВтЗЈЁЗ

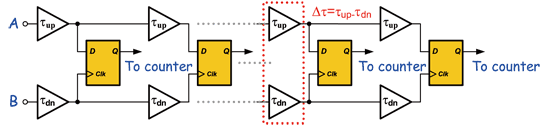

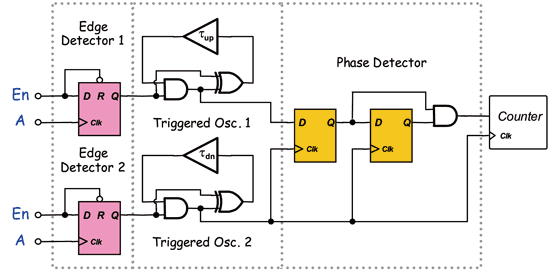

гЮБъбгГйЯпЃЈVernier Delay LineЃЛVDLЃЉЮЊФПЧАзюГЃБЛВЩгУЕФЖЖЖЏВтЪдММЪѕЃЌгЩPiotr Dudekгк2000 JSSCЫљЗЂБэЁЃВйзїдРэЪЧНЋВЮПМгыД§ВтЪБТіЗжБ№ЫЭШыСНИіВЛЭЌбгГйСПЃЈτupгыτdnЃЉЕФdelay chainжаЃЌШєСНепМфгаЖЖЖЏСПДцдкЃЌОбгГйЕЅдЊКѓЦфЛсЯрЛЅБЦНќЁЃЕБдкnИіжмЦкКѓСНбЖКХЭЌЯрЮЛЛђЪЧЯрЮЛСьЧАЁЂТфКѓЕФзДЬЌИФБфЃЌМДПЩЫуГіЖЖЖЏСПЮЊnxЁїτЃЌЕБжаЁїτ=τup-τdnЁЃЫљвдНхгЩДЫВтЪдММЪѕНЋПЩВтЪдЕЭгкДЮТпМеЂЃЈsub-gateЃЉЕФЖЖЖЏСПЁЃ

гХЕуЃК

ЁёЪЙгУбгГйЪБМфВюЕФЙлФюРДЪЕЯжЃЌПЩОпгаНЯМбЕФВтЪдНтЮіЖШЃЈ=ЁїτЃЉЁЃ

ШБЕуЃК

ЁёжЦГЬБфвьЯТЮоЗЈШЗБЃУПИібгГйЕЅдЊжЎбгГйЪБМфСПЯрЕШЃЌДЫНЋгАЯьВтЪдзМШЗЖШЁЃ

ADC Sampling [4]

ЁЖЭМЫФ ЪЙгУADC samplingжЎЖЖЖЏСПВтЗЈЁЗ

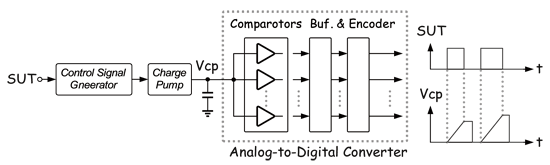

вђЖЖЖЏЮЊЪБМфЕФБфЛЏЃЌЫљвдвЛАуВтЪдМмЙЙЖМЪЧДгЪБМфЙлФюРДЕУжЊЁЃЕЋHenery C. Linгк2003 ITCжаЃЌРћгУЪБМфзЊЕчбЙЕФЗНЪНРДЪЕЯжЖЖЖЏСПВтЪдЁЃМђЕЅРДПДетОЭЪЧвЛзщЕчКЩАяЦжЃЌЕБД§ВтбЖКХЮЊИпЕчЮЛЪБЕчСїЛсЖдИКдиГфЕчЃЛЖјдкЕЭЕчЮЛЪБОЭНЋЕчбЙЮЛзМжижУЙщСуЁЃЫљвдД§ВтбЖКХТіВЈПэЖШдНДѓЃЌЫљЕУЕФЕчбЙжЕвВОЭдНИпЃЛЗДжЎТіВЈПэЖШНЯаЁЕчбЙвВОЭЫцжЎНЕЕЭЁЃНгзХдйРћгУADCНЋЕчбЙЮЛзМзЊЛЛГЩЪ§ЮЛТывдЧѓЕУЖЖЖЏСПЁЃ

гХЕуЃК

ЁёгкЕЭЫйЪБТіВтЪджаОпгаНЯИпжЎНтЮіЖШЁЃ

ЁёВЩгУreal timeЕФЪфГіЃЌВтЪдЪБМфНЋПЩЫѕЖЬЁЃ

ШБЕуЃК

ЁёВтЪдНтЮіЖШгыВтЪдЫйЖШНдШЁОігкADCжЎЩшМЦЁЃ

ЁёгкЕЭбЙВйзїЪБвзЪмДЙжБЖЖЖЏгАЯьНјЖјЕМжТНтЮіЖШДѓЗљЯТНЕЁЃ

Component-Invariant VDL [5]

ЁЖЭМЮх ЪЙгУcomponent-invariant VDLжЎЖЖЖЏСПВтЗЈЁЗ

зюКѓвЛжжВтЪдМмЙЙЮЊG. W. Robertsгк2001 ITCЫљЬсГіЁЃДЫжжВЩгУЗЧБфвьСПдЊМўжЎгЮБъбгГйЯпКЭ[03]ЕФзіЗЈЦфЪЕЗЧГЃЯрЫЦЁЃЦфЪЧРћгУвЛМЖЕФбгГйЕЅдЊШЛКѓШУбЖКХЛиЪкеёЕДЃЌШчДЫвЛРДНЋПЩШЗБЃСПВтНтЮіЖШНдЮЊЁїtЁЃШєгкnИіеёЕДжмЦкКѓСНИібгГйСПЯрЮЛИФБфЛђЪЧЯрЭЌЪБЃЌдђПЩвР[03]ЕФзїЗЈМЦЫуГіЖЖЖЏСПЁЃ

гХЕуЃК

ЁёУПМЖбгГйНдЮЊЁїtЃЌЬсЩ§СПВтзМШЗЖШЁЃ

ЁёЪЙгУСНИібгГйСПжЎВюРДСПВтЖЖЖЏСПЃЌвђДЫПЩОпгаНЯИпНтЮіЖШЁЃ

ШБЕуЃК

ЁёКЭ[02]МмЙЙвЛбљашНЯГЄЕФВтЪдЪБМфЁЃ

гЩвдЩЯЫљЬсГіЕФЮхжжВтЪдЗЈПЩПДГіЃЌвдФПЧАЕФВтЪдММЪѕЖјбдЃЌВЛЭтКѕЪЧРћгУsignal amplitude samplingвдМАtime domain analysisСНжжЗНЗЈРДЪЕЯжЁЃЕЋвдЧАепРДЫЕЃЌЫцзХжЦГЬНјВНВйзїЕчбЙНЕЕЭЃЌДЫзїЗЈНЋУцСйADCЩшМЦЕФЦПОБЃЌЫљвдНќФъРДвбНЯЩйШЫВЩгУДЫзїЗЈРДЪЕЯжЖЖЖЏСПВтЪдЁЃКѓепЫфИїМмЙЙЪЕМљЗНЪНгаЫљВЛЭЌЃЌЖрЪ§ЪЧРћгУЪБМфЪ§ЮЛзЊЛЛЃЈTime-to-Digital ConvertedЃЉЕФЙлФюРДЪЕЯжЁЃШЛЖјетаЉМмЙЙЖМгаЙВЭЈЕФЮЪЬтЃЌОЭЪЧВйзїЫйТЪВЛПьвдМАНтЮіЖШВЛИпЁЃвдФПЧАЪаУцЩЯPCжмБпВњЦЗРДЫЕЃЌЦеБщЫйЖШНдЪєгкМИАйMHzЕШМЖЃЌЖјCPUЛђЪЧДЋЪфНщУцдђЛсЩЯПДжСGHzЕШМЖЁЃСэЭтЖЖЖЏСПдкИпЫйЯЕЭГжазюДѓжЕдМЖЈвхдкЪ§ЪЎpsЃЌЫљвдШєВтЪдЯЕЭГУЛгаКУЕФНтЮіЖШКЭПэЗЖЮЇВтЪджЎФмСІЃЌНЋЮоЗЈХаБ№Д§ВтбЖКХжЎКУЛЕЁЃвђДЫБОЮФНЋЬсГівЛИіаТЕФЖЖЖЏВтЪдЯыЗЈгыМмЙЙЃЌеыЖдИпЫйгыЕЭЖЖЖЏЪБТізїИќОЋШЗЃЈprecisionЃЉгыИќзМШЗЃЈaccuracyЃЉжЎЖЖЖЏВтЪдЁЃ

Proposed Technique

ЁЖЭМСљ ДЋЭГЪБМф-Ъ§ЮЛзЊЛЛЙ§ГЬжЎЪОвтЭМЁЗ

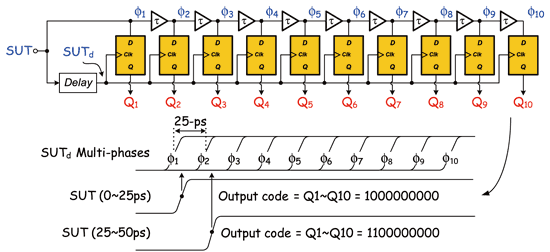

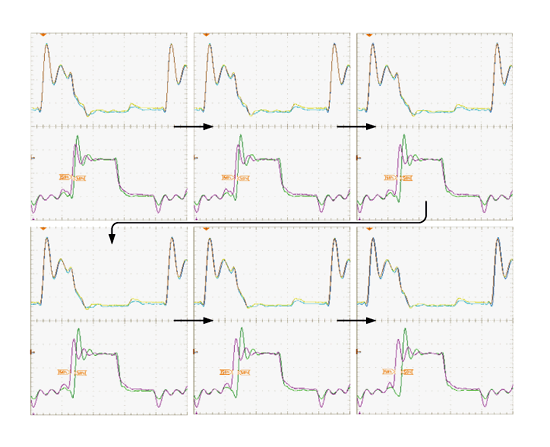

дкНщЩмЮвУЧЫљЬсГіжЎВтЪдЗНЗЈЧАЃЌЯШРДЬНЬжДЋЭГВтЪдЕФЮЪЬтЁЃЭМСљЮЊДЋЭГЪБМф-Ъ§ЮЛзЊЛЛЕФЙ§ГЬЁЃЕБвЛЪБТіЃЈSUTЃЉЗЂЩњЖЖЖЏЪБЃЌЦфБпдЕЛсРыПЊдБОРэЯыЕФЮЛжУЃЌДЫЪБЦеБщЕФзіЗЈЛсНЋSUTбгГйвЛИіжмЦкЪБМфЃЈSUTdЃЉКѓШЅВтСПEnКЭEn+1БпдЕжЎЖЖЖЏГЬЖШЁЃЖјВтЪдЗНЗЈОЭЪЧНЋSUTЫЭШыdelay chainжаЕБзїБЛШЁбљЕФзЪСЯЃЌЖјSUTdдђзїЮЊШЁбљЪБТіЁЃЕБSUTdЖдОЙ§ВЛЭЌбгГйСПжЎSUTзіШЁбљКѓМДЛсВњЩњГіЮТЖШТыЃЈthermal codeЃЉЕФЪ§ЮЛзЪСЯЃЌДЫЪфГізЪСЯМДДњБэВЛЭЌЪБТіЖЖЖЏСПЁЃ

ОйР§РДЫЕЃЌШєФПЧАdelay chainЮЊ10МЖ25-psбгГйСПжЎбгГйЕЅдЊЫљзщГЩЃЌДЫЪБЪБТіжмЦкЖджмЦкЖЖЖЏСПЮЊ10-psЃЌОШЁбљКѓЛсЕУЕН1000000000ЕФЪ§ЮЛТыЃЛЖјШєЕБЖЖЖЏСПЮЊ30-psЃЌдђЛсВњЩњ1100000000ЁЃвђДЫЖЖЖЏСПдНДѓЃЌЪ§ЮЛТыжаЕФ1вВОЭЛсдНЖрЁЃЫљвдФПЧАЕФММЪѕНдЪЧвдДЫжжЯыЗЈРДЪЕЯжЖЖЖЏСПВтЪдЃЌЖјВЛЭЌжЎДІОЭЪЧЛсРћгУаэЖрЕчТЗММЧЩНЋбгГйЕЅдЊЕФбгГйСПЫѕаЁвдЬсИпВтЪдНтЮіЖШЃЌШчгЮБъбгГйЯпЁЂФкВх…ЕШЁЃ

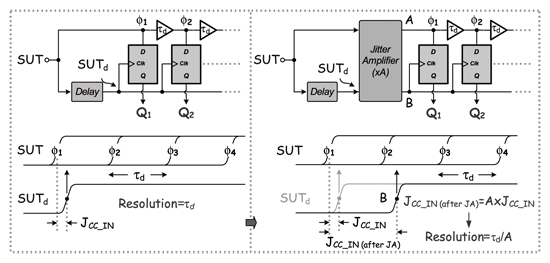

ЕЋДгЩЯЪіЫЕУїМДПЩЕУжЊЃЌвђЮЊНтЮіЖШКЭбгГйЕЅдЊжЎбгГйСПГЩЗДБШЃЌЫљвдШєВЛНЋбгГйСПЩшМЦЕУЗЧГЃаЁЃЌЯрЖдЕиОЭЛсВњЩњВтЪдЮѓВюСПЁЃвдЧАР§РДЫЕЃЌРэЯыЩЯЕБЖЖЖЏСПЮЊ0.1-psКЭ24.9-psЪБЫљЕУЕНЕФЪ§ЮЛТыНдЮЊ1000000000ЃЌЦфзюДѓЮѓВюСПНгНќвЛИібгГйЪБМфЁЃЫљвдЫЕШєдкИпЫйЕЭЖЖЖЏЕФгІгУжаЃЌДЫВтЪдЮѓВюСПНЋЮоЗЈЫЕЗўВтЪдЪЙгУепЁЃЕЋМйШєРћгУЕчТЗЩЯЕФММЪѕЫѕЖЬбгГйЪБМфМѕЩйЮѓВюСПЃЌЦфЛЙЪЧЛсвђжЦГЬЯожЦгаМЋЯожЕДцдкЃЌЧвЭЈГЃЛсКФЗбНЯДѓЕФгВЬхУцЛ§ЁЃЫљвдЮвУЧЗДЯђЫМПМЃЌВЛвдЪБМф-Ъ§ЮЛзЊЛЛЦїЮЊГіЗЂЕуЃЌЖјЪЧвдвЛМђЕЅЕчТЗММЪѕЯШЗХДѓжмЦкЖджмЦкжЎЖЖЖЏСПЃЌШчДЫвЛРДМДПЩМѕЩйВтЪдЕчТЗЩшМЦЕФРЇФбЖШВЂЬсЩ§ВтЪдНтЮіЖШЁЃ

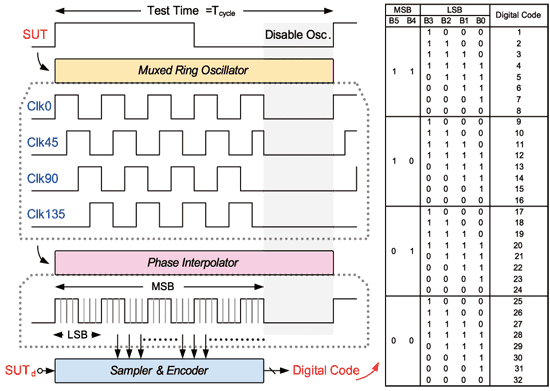

ЁЖЭМЦп ЖЖЖЏСПЗХДѓжЎИХФюЭМЁЗ

вдЭМЦпЮЊР§ЃЌШєбгГйЕЅдЊЕФбгГйЪБМфЮЊτdЃЌдђДњБэдкЮоШЮКЮИЈжњЕчТЗЯТЦфзюМбНтЮіЖШМДЮЊτdЁЃЕЋвдЫљЬсГіЕФЙлЕуРДПДЃЌШєДЫЪБЯШНЋЪфШыЖЖЖЏСПЗХДѓAБЖЫЭШыdelay chainжаЃЌаЇЙћОЭШчЭЌНЋбгГйЪБМфЫѕЖЬРДдіМгВтЪдНтЮіЖШЃЌвВДњБэДЫЪБећИіМмЙЙзюМбНтЮіЖШБуПЩЕШаЇГЩ”τd/A”ЁЃ

ОйР§РДЫЕЃЌгк0.13-umжЦГЬжазюаЁеЂбгГйЪБМфЮЊ25-psЃЌЫљвдВЩгУДЋЭГзїЗЈДѓдМжЛФмСПВтЕНЕФЖЖЖЏСПЮЊ25-psЃЛЕЋЪЧШєдкЖЖЖЏСПзЊЛЛГЩЪ§ЮЛТыЧАЯШНЋЦфЗХДѓ25БЖЃЌдђзюМбНтЮіЖШМДЬсЩ§жС1-psЃЈ25-ps/25ЃЉЁЃГ§ДЫжЎЭтЃЌЫцзХЖЖЖЏЗХДѓБЖТЪAДѓгкτdКѓЃЌвђбгГйЕЅдЊЕФбгГйЪБМфаЁгк1-psЃЈτd/A<1ЃЉЃЌЫљвдДЫЪБНЋПЩеыЖдsub-pico-secondЕШМЖжЎЖЖЖЏСПзїВтЪдЁЃ

вђДЫБОЖЖЖЏВтЪдИХФюОЭЪЧНхгЩЗХДѓЪфШыЪБТіжмЦкЖджмЦкжЎЖЖЖЏСПЃЌНјЖјВЙзуЪБМф-Ъ§ЮЛзЊЛЛЕчТЗЕФВЛзуЃЌЧвИќНјвЛВНЬсЩ§ВтЪдНтЮіЖШЃЌвдШУДЫВтЪдЯЕЭГВйзїгкИпЫйЕЭЖЖЖЏСПЕФЯЕЭГОпгаМЋМбзМШЗЖШЁЃЭМАЫМДЮЊдЫгУЫљЬсГіжЎЖЖЖЏЗХДѓдРэЫљЪЕЯжЕФФкНЈЪБТіЖЖЖЏСПжЎВтЪдМмЙЙЁЃ

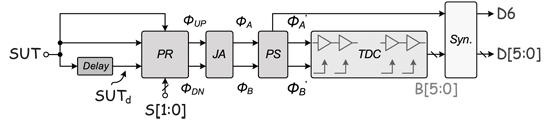

ЁЖЭМАЫ ЫљЬсГіжЎФкНЈЪБТіЖЖЖЏСПВтЪдМмЙЙЁЗ

ЦфАќКЌСЫТіВЈЭЬЪЩЕчТЗЃЈPulse RemoverЃЛPRЃЉЁЂЖЖЖЏЗХДѓЕчТЗЃЈJitter AmplifierЃЛJAЃЉЁЂЯрЮЛбЁдёЕчТЗЃЈPhase SelectorЃЛPSЃЉЁЂЪБМф-ЪфЮЛзЊЛЛЕчТЗЃЈTime-to-Digital ConverterЃЛTDCЃЉгыЭЌВНЕчТЗЃЈsynchronizerЃЉЁЃЦфжаPRКЭJAжЎзщКЯЪЧгУРДНЋЪфШыЖЖЖЏСПзіЯпадЗХДѓЃЛЖјTDCЕФЙІгУдђПЩАбЖЖЖЏСПЛЏГЩЪ§ЮЛТыЃЛСэЭтЭЌВНЕчТЗЛсНЋЫљгаЕФЪфГіЪ§ЮЛТызїЭЌВНвдРћКѓајШэЬхЛђгВЬхжЎЗжЮіЁЃЕЋдкДЫЪфГіжЛПДЕФГіжмЦкЖджмЦкМфжЎЖЖЖЏСПЃЌВЂЮоЗЈХаЖЯФПЧАБпдЕМфЕФЙиЯЕЃЈМДЯрЮЛЃЉЁЃ

вђДЫгкTDCЧАВхШывЛPS[6]ЃЌЦфгУгкХаЖЯФПЧАЯрЮЛЙиЯЕВЂОіЖЈΦAгыΦBНјШыTDCЧАЫЕБзїзЪСЯЖјЫЕБзїШЁбљЪБТіЁЃШєΦAСьЧАΦBЃЌдђD6ЮЊHiЁЂΦA’=ΦAЁЂΦ’=ΦBЁЂЪєгке§ЯђЖЖЖЏЃЛЗДжЎШєΦBСьЧАΦAЃЌдђD6ЮЊLowЁЂΦA’=ΦBЁЂΦB’=ΦAЁЂЪєгкЗДЯђЖЖЖЏЁЃРћгУДЫЮЛдЊжЎНсЙћНЋПЩИќУїШЗХаЖЯЖЖЖЏжЎаЭЬЌЁЃНгЯТРДЮвУЧОЭеыЖдИїжївЊЕчТЗзіНјвЛВПЕФНщЩмЁЃ

ЖЖЖЏЗХДѓЕчТЗЩшМЦМмЙЙ [7] [8]

ЁЖЭМОХ ЖЖЖЏЗХДѓЕчТЗжЎМмЙЙЭМгыЪБађЭМЁЗ

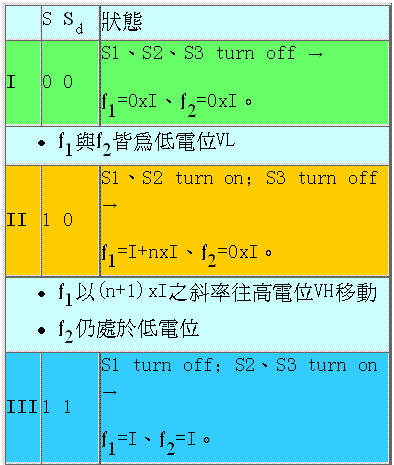

жмЦкЖджмЦкЖЖЖЏСПМДЮЊКѓвЛИіжмЦкБпдЕEn+1КЭЧАвЛИіжмЦкБпдЕEnжЎЯрЮЛЮѓВюЃЌвђДЫШєвЊЪЕЯжЖЖЖЏСПЗХДѓОЭБиашНЋEnКЭEn+1МфжЎБпдЕЪБМфВюРДѓЁЃдкБОЮФжаНЋВЩгУЕчСїЖдИКдиГфЗХЕчжЎдРэРДДяЕНЖЖЖЏЗХДѓжЎЙІФмЁЃЮвУЧвдЭМОХРДЫЕУїЦфВйзїдРэЁЃ

ЖЖЖЏЗХДѓЕчТЗЛљБОЩЯЪЧгЩСНзщВЛЭЌЕчСїСПжЎЕчКЩАяЦжЃЈCharge PumpЃЛCPЃЉгыОіВпЕчТЗЃЈDecision CircuitЃЛDCЃЉЫљзщГЩЃЌЖјЗжБ№гЩД§ВтбЖКХSUTЁЂвЛИіжмЦкбгГйКѓжЎбЖКХSUTdгыСНепжЎзщКЯРДПижЦЁЃЦфзюЛљБОЕФЯыЗЈЮЊРћгУВЛЭЌГфЕчаБТЪЃЈМДГфЕчЫйЖШЃЉДюХфбЖКХВЛЭЌЦ№ЪМЕуЃЈМДзЊЬЌБпдЕЃЉжЎЬиадЃЌРДКЯГЩГіОпгаНЯДѓЖЖЖЏСПЕФЪБТіБпдЕЁЃЖјЮЊСЫЧхГўНтЪЭЦфЗХДѓдРэЃЌЮвУЧНЋSUTЃЈSЃЉгыSUTdЃЈЃЈSdЃЉвРЯрЮЛЙиЯЕЧјЗжГЩЫФИіЧјМфЃЌШЛКѓЗжБ№ЬНЬждкВЛЭЌЧјМфФкЕФВйзїЧщаЮЁЃШчБэвЛЫљЪОЁЃ

(БэвЛ) ЕчКЩАяЦжВйзїзДЬЌБэ

ДюХфЭМОХгыБэвЛжЎа№ЪіЃЌДгжаПЩвдЕУжЊдкГѕЪМзДЬЌЪБвђSUTгыSUTdЮЊЕЭЕчЮЛЃЌПЊЙиНдturn offЃЌЫљвдВЂЮоШЮКЮЕчСїЖдИКдизіГфЕчвђДЫЪфГіНсЙћЃЈf1ЁЂf2ЃЉНЋЮЊЕЭЕчЮЛЃЈVLЃЉЁЃЕЋШєЕБСНИіphaseМфгаЖЖЖЏДцдкЪБЃЌSUTЛсЮЊИпЕчЮЛЖјSUTdЮЊЕЭЕчЮЛЁЃДЫЪБf1ЛсвдЃЈn+1ЃЉБЖЕФЕчСїЖдИКдиГфЕчpull upЃЌЖјf2вђS3 turn offЫљвдНЋБЃГжЧАвЛзДЬЌЕФЕЭЕчЮЛЁЃНгзХОЙ§ΔτЕФЪБМфКѓЃЌSUTdвВpull highЃЌДйЪЙS3 turn onЁЂS1 turn offЃЌДЫЪБf1КЭf2НЋвЛЦ№вдIЕФЫйЖШЭљИпЕчЮЛвЦЖЏЁЃЕЋЪЧзаЯИЙлВьRegion IIКЭRegion IIIжЎЙ§ГЬЃЌвђдкΔτЕФетЖЮЪБМфРяf1ЯШвдНЯПьЕФЫйЖШЦєЖЏЃЌШєRegion IIIдкЯрЭЌГфЕчЕФаБТЪЬѕМўЯТЃЈЕчСїСПНдЮЊIЃЉЦфЛсЯШЕНДяЮШЬЌЮЛзМЃЛЖјНгзХдйОЙ§n*ΔτЪБМфКѓЃЌf2ВХвВЛсЕНДяДЫЮЛзМЁЃДЫЪБДгЭМОХжаПЩвдПДГіf1ЁЂf2гыЫљЩшЖЈЕФСйНчЕчбЙЃЈVthЃЉгаСНИіНЛЕуЃЌШєгУСНзщОіВпЕчТЗНЋзЊЬЌЕуХаЖЯГіРДМДПЩВњЩњСНзщВЛЭЌЯрЮЛВюЕФЪфГібЖКХЃЈOut1ЁЂOut2ЃЉЁЃЫљвдРћгУЩЯЪіжЎЬѕМўЃЌЮвУЧПЩвдМђЕЅвдЙЋЪНвЛРДБэЪОГіЪфГігыЪфШыМфЕФЙиЯЕЃК

ЁЖЙЋЪНвЛЁЗ

ЦфжаfOUTЮЊOut1ЁЂOut2МфЕФЯрЮЛВюЃЈЗХДѓКѓжЎжмЦкЖджмЦкЖЖЖЏСПЃЉЁЂfINЮЊSUTЁЂSUTdМфЕФЯрЮЛВюЃЈЗХДѓЧАжЎжмЦкЖджмЦкЖЖЖЏСПЃЉЃЌЖјAМДДњБэЗХДѓБЖТЪЁЃ

РћгУЩЯЪіИХФюЃЌБОДДзїМДПЩНЋЪБТібЖКХжЎжмЦкЖджмЦкЖЖЖЏСПМгвдЗХДѓЃЌРДУжВЙЪБМф-Ъ§ЮЛзЊЛЛЕчТЗЕФВЛзуЁЃШЛЖјЕЅДПЙтППЕчСїГфЕчФмСІЕФааЮЊФЃЪНРДДяГЩЗХДѓФПЕФЃЌЛсУцСйЕчТЗВйзїЦПОБНјЖјЕМжТВтЪдЮѓВюВњЩњЃЌР§ШчЗХДѓБЖТЪЕФЗЧЯпадЛђЪЧВйзїЦЕТЪБфЛЏЕШЃЌНгЯТРДЮвУЧЛсеыЖдетаЉаЇгІЬсГіНтОіжЎЕРЁЃ

ЖЖЖЏЗХДѓЕчТЗМАPulse RemoverЩшМЦЕФЗжЮі

(БэЖў) ЗћКХБэЪО

дкЖЖЖЏЗХДѓЕчТЗЛљБОЩшМЦжаЃЌвђЮЊЪЧЪЙгУЕчСїЖдИКдиГфЗХЕчжЎЫйТЪРДДяЕНЖЖЖЏЗХДѓЃЌвђДЫЯШеыЖдГфЗХЕчЮЛзМвдМАЪБМфзїЖЈвхЁЃШчБэЖўЫљЪОЁЃ

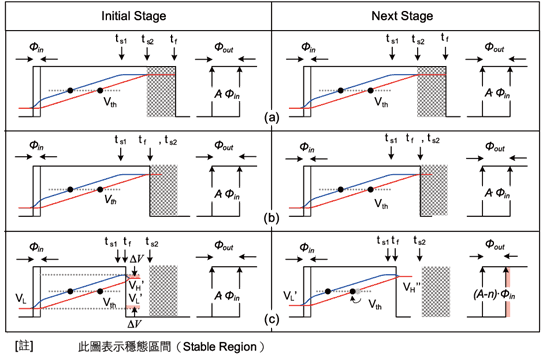

ЭМЪЎ(a)жаЃЌЭЈГЃЖЖЖЏЗХДѓЕчТЗдкЕЭЫйТЪВйзїЪБЃЌвђЦфЖЖЖЏСПЯрНЯгкАыИіжмЦкЪБМфЫљеМЕФБШР§НЯаЁЃЌвђДЫЕчКЩАяЦжЪфГіЃЈf1ЁЂf2ЃЉЕНДяИпЮШЬЌЕуЪБМфЃЈts1ЁЂts2ЃЉЭЈГЃЛсаЁгкИКдЕзЊЬЌЕуЪБМфtfЁЃ

ЁЖЭМЪЎ ЖЖЖЏЗХДѓЕчТЗЪБађЭМЃК(a)Case 1 : tf>ts2ЃЛ(b)Case 2 : tf≈ts2ЃЛ(c)Case 3 : tf

ЫљвддкДЫЦЕЖЮВйзївђгазуЙЛЕФЮШЬЌЧјМфЃЈstable regionЃЉЃЌЦфООіВпЕчТЗКѓВњЩњжЎЪфГіЯрЮЛВюfOUTЯрНЯгкЪфШыЯрЮЛВюfINМИКѕФмЮЌГжЖЈжЕЃЌвВОЭДњБэЗХДѓБЖТЪAЮЊconstantЁЃЕЋШєЕБД§ВтЪБТіЦЕТЪЩЯЩ§КѓЃЌШчЭМЪЎ(b)ЫљЪОЃЌЫцзХбЖКХжмЦкЫѕЖЬtfжЎЗЂЩњЕуЬсЧАЃЌдкtfЗЧГЃНгНќЕЋДѓгкts2ЪБЃЌЖЖЖЏЗХДѓЕчТЗвРШЛПЩУуЧПЮЌГжзЁЗХДѓБЖТЪЃЌЫљвдДЫЪБМДГЦЮЊВйзїСйНчжЕЁЃЕЋМйШєВЛавдкЫљЪЙгУЕФгІгУжаtfЗЂЩњНЯДѓЕФБфвьЛђЪЧВйзїЦЕТЪМЬајЭљЩЯЩ§ЃЌЕМжТts2БШtfЭэЗЂЩњЃЌдђЗХДѓБЖТЪНЋПЊЪМВњЩњЗЧЯпадЕФБфЛЏЁЃ

ДгЭМЪЎ(c)ПЩЙлВьГідке§ГЃЕФВйзїФЃЪНЯТf1гыf2зюКѓНдЛсЛиЕНЮШЬЌЮЛзМVHЁЂVLЁЃЕЋМйШєзЊЬЌБпдЕtfдкЩаЮДЮШЖЈЧАОЭГіЯжЃЌдђf1гыf2жЎЕчбЙЛсБЛЧПжЦЮЌГждкаТЕФЮЛзМЩЯЃЌвВОЭЪЧVH’ЃЈ=VH-ΔVЃЉгыVL’ЃЈ= VL +ΔVЃЉЁЃетИіЯжЯѓЫфЖдгкЕквЛИіжмЦкЃЈinitial stageЃЉжЎЗХДѓБЖТЪУЛгадьГЩгАЯьЃЌЕЋЪЧДгЭМжаЕУжЊЃЌдкЯТвЛИіжмЦкЃЈnext stageЃЉжавђЮЊf1ЁЂf2ЕчбЙЦ№ЪМЮЛзМЕугаСЫБфЛЏЃЌЫљвдОГфЕчКѓгыСйНчЕчбЙVthЕФНЛЕуБиШЛЫцжЎИФБфЁЃЛЛОфЛАЫЕОЭЪЧvoltage domain variationНЋзЊЛЛГЩtime domainжЎphase errorЃЌДЫЪБМДЛсдьГЩЗХДѓБЖТЪБфЖЏЁЃвђДЫжмЦкЖджмЦкЖЖЖЏЗХДѓЕчТЗашВйзїдкwide rangeжЎгІгУЪБЃЌОЭБиашРћгУвЛаЉЛњжЦПижЦЮШЬЌЪБМфЕуtsБШИКдЕзЊЬЌЕу tfдчЗЂЩњЃЌШчДЫВХВЛЛсдьГЩЗХДѓБЖТЪЕФЪЇецЁЃгаМјгкДЫЃЌБОЮФНЋЬсГівЛИіЪЙгУТіВЈЭЬЪЩЙлФюжЎЕЅпЂШЁСПВтЗНЪНРДИФЩЦжЎЁЃ

ТіВЈЭЬЪЩжЎЕЅпЂШЁСПВтЗНЪН

ЁЖЭМЪЎвЛ ТіВЈЭЬЪЩИХФюЭМЁЗ

вдЩЯЪіЬжТлПЩжЊЃЌШєвЊЪЕЯжtsfЃЌВЛЭтКѕЪЧНЋЮШЬЌЪБМфЕуЭљЧАРЛсЛђепЪЧбгГйИКдЕзЊЬЌЕуВњЩњжЎЪБМфЁЃвдЕчТЗЪЕЯжНЧЖШЖјбдЃЌвђtsЪЧЕчСїЖдИКдиГфЕчКѓЫљВњЩњЕФЕчбЙгыИпЕчЮЛVHжЎНЛМЏЃЌЫљвдЕчСїдНДѓЁЂЛиЕНЮШЬЌЕуФмСІдНЧПЃЌЯрЖдЦфГіЯжЪБМфЛсдНдчЁЃЕЋЖЖЖЏЗХДѓЕФВњЩњОЭЪЧНхгЩВЛЭЌЫйТЪЕчСїжЎВюЫљЕУЃЌЯыБиШЛЗХДѓБЖТЪвВНЋЪмЕНгАЯьЁЃЫљвдЮЊСЫМцЙЫЗХДѓБЖТЪгыЕчСїСПМфtrade-offЃЌБОЮФНЋВЩгУбгГйtfжЎзїЗЈРДЮЌГжВЛЭЌВйзїЦЕТЪЯТЕФЖЖЖЏЗХДѓБЖТЪЁЃ

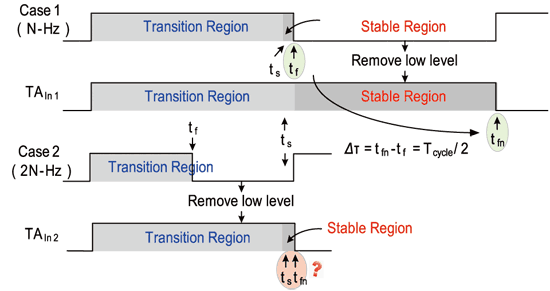

ШчЭМЪЎвЛcase1ЫљЪОЮЊвЛЕЭЦЕВйзїЪБЕФЪОвтЭМЁЃЮЊСЫШУЖЖЖЏЗХДѓЕчТЗЕФЗХДѓБЖТЪЮЌГжЖЈжЕЃЌД§ВтбЖКХЕФtsБиашаЁгкtfЃЌЖјworst caseЛсЗЂЩњдкtsЕШгкtfЕФЪБМфЕуЃЌДЫЪБЮШЬЌЧјМфМИКѕЛсНќЫЦгкСуЃЌвВОЭЪЧЫЕЗХДѓБЖТЪЛсЗЧГЃВЛЮШЖЈЁЃ

ЮЊСЫИФЩЦетИіЮЪЬтЃЌвдЯШЧАЕФЫЕЗЈОЭБиашНЋtfЪБМфЕузібгГйЁЃМђЕЅРДПДОЭЪЧАбВтЪдЫйЖШЗХТ§ЃЌРћгУТіВЈЭЬЪЩЕчТЗвЦГ§Еє0.5ИіжмЦкЃЌРДЛЛШЁЮШЬЌЧјМфжЎПэЖШЁЃШчЭМЫљЪОЃЌШєАбcase1ЕФбЖКХзіДІРэКѓГЩЮЊTAIn1ЃЌЦфИКдЕзЊЬЌЪБМфЕуЗЂЩњЕФЪБМфЭљКѓбгГйСЫΔτЃЈ=tfn-tf=Tcycle/2ЃЉЃЌетДњБэзХЮШЬЌЧјМфЫцжЎЗХДѓ2БЖЁЃвђДЫШєАбД§ВтбЖКХЕФЦЕТЪдіМгКѓЃЌЦфвђОпгазуЙЛЕФЮШЬЌЪБМфЃЌЫљвдЗХДѓБЖТЪНЋВЛЪмЕНclock variationКЭЦЕТЪБфЖЏжЎгАЯьЁЃ

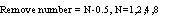

ЕЋдкЭМЪЎвЛ Case2жаЃЌД§ВтЪБТібЖКХВйзїЫйЖШГжајЩЯЩ§ЃЈдМЮЊCase1ЕФСНБЖЃЉЃЌПЩвдКмУїЯдЙлВьЕНШєВЛВЩгУТіВЈЭЬЪЩЛњжЦЃЌtsвбдЖдЖГЌдНСЫtfЃЌДЫЪБЖЖЖЏЗХДѓЕчТЗжЎЗХДѓБЖТЪвбЮЊЗЧЯпадВйзїЃЛЕЋШєМгШыТіВЈЭЬЪЩЕФЛњжЦКѓЃЌвђД§ВтбЖКХЫйЖШЬЋПьЃЌдкЯрЭЌГфЗХЕчЕФЫйТЪЬѕМўЯТЃЌtsвВЗЧГЃППНќtfnЃЌЗХДѓБЖТЪБфвьЕФЮЪЬтЛЙЪЧДцдкЁЃЫљвдгЩДЫПЩжЊеце§вЊДяЕНwide rangeЕФВйзїЃЌВЛЙмдкШЮКЮЦЕТЪЯТЃЌНдашвЊгЕгаЯрЭЌЕФЮШЬЌЧјМфЃЌВХЛсеце§ЕУЕНconstantжЎЗХДѓБЖТЪЁЃгаМјгкДЫЃЌЮвУЧНЋТіВЈЭЬЪЩЕФЛњжЦЩдзіаоИФЃЌНЋВЛдйЮЌГжЙЬЖЈвЦГ§0.5ИіжмЦкЃЌЖјЪЧЫцзХД§ВтЮяЕФЦЕТЪУПдіМгвЛБЖЖјЫцжЎБфЛЏЃЌЦфremove numberПЩгЩЙЋЪНЖўБэЪОжЎЃК

ЁЖЙЋЪНЖўЁЗ

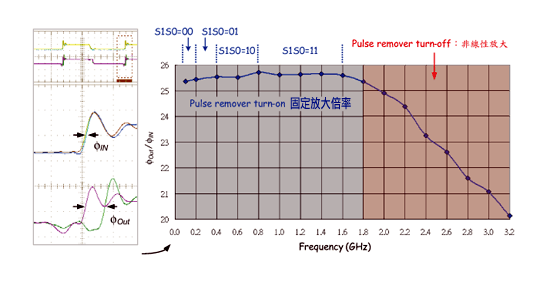

ЦфжаNЮЊЦЕТЪБфЛЏТЪЁЃдкБОЮФжаЫљЬсГіЕФР§згвђЮЊвЊДяЕНЪ§ЪЎMHz~1.6GHzжЎВйзїЃЌЫљвдНЋ100MHzЖЈЮЊЛљзМЃЌЦЕТЪУПдіМгвЛБЖОЭБиашИФБфremove numberРДЮЌГжЗХДѓБЖТЪЁЃШчЭМЪЎЖўЫљЪОЁЃ

ЁЖЭМЪЎЖў гкИїВйзїЦЕЖЮМфжЎТіВЈЭЬЪЩИХФюЭМЁЗ

вдЕчТЗЕФНЧЖШЖјбдЃЌвЊЪЕЯжЭМЪЎЖўТіВЈЭЬЪЩЕчТЗЦфЪЕВЛФбЃЌжЛвЊНЋД§ВтбЖКХвРЦЕЖЮОЙ§ЯрЖдгІЕФГ§ЦЕЦїМДПЩЪЕЯжЁЃЕЋЪЕМЪЩЯШєжБНгАбД§ВтбЖКХОЙ§Г§ЦЕЦїРДДяЕНТіВЈЭЬЪЩЃЌвРВЮПМЮФЯз[9]жЎЫЕЗЈЃЌИУбЖКХЕФЖЖЖЏвВЭЌЪБМфЛсБЛЗХДѓЃЌдМЮЊ √nБЖЁЃДЫЭтЃЌГ§16ЕФЕчТЗзюЩйашвЊ4зщDFFРДЪЕЯжЃЌДњБэД§ВтбЖКХЕНДяЖЖЖЏЗХДѓЕчТЗЧАОЭБиашОЙ§аэЖрtransistorЃЌНјЖјЪмЕНpower noiseЛђЪЧthermal noiseИЩШХЕМжТЖЖЖЏЩЯЩ§ЃЌетНЋЛсбЯжигАЯьСПВтзМШЗЖШЁЃ

вдБпдЕМьВтДяЕНТіВЈЭЬЪЩаЇЙћ

ЁЖЭМЪЎШ§ (a)ЫљЬсГіжЎЖЖЖЏЗХДѓЕчТЗЃЛ(b)БпдЕМьВтЕчТЗВйзїЪОвтЭМЁЗ

вђДЫБОЮФНЋВЩгУБпдЕМьВтЃЈedge detectionЃЉжЎММЪѕРДДяЕНТіВЈЭЬЪЩЕФаЇЙћЃЌШчЭМЪЎШ§(a)ЫљЪОЁЃЦфжївЊАќКЌСНДѓЗНПщЃКБпдЕМьВтЦїгыТіВЈЭЬЪЩЕчТЗЁЃЪзЯШЃЌЕБД§ВтбЖКХЦєЖЏКѓЃЌЮЊСЫЮЌГжЗХДѓБЖТЪЃЌашЯШНјааpulse removeЕФЖЏзїЁЃвдЭМЪЎШ§(b)ЮЊР§ЃЌSUTЮЊД§ВтбЖКХЃЌENЮЊТіВЈЭЬЪЩЕчТЗЫљВњЩњЃЌEЮЊОЙ§ДІРэКѓЕФД§ВтбЖКХЁЃЦфжаТіВЈЭЬЪЩЕчТЗЪЧгЩMUXЫљЪЕЯжЃЌЦфПЩНхгЩПижЦsНХЮЛРДбЁдёENбЖКХЮЊSUTжЎ/2ЁЂ/4ЁЂ/8ЁЂ/16ЕФНсЙћЁЃ

ДЫЭтENНгжСБпдЕМьВтЦїЕФdata inputЖЫЃЌЖјSUTдђНгжСclock inputЖЫЁЃЕБENЮЊИпЕчЮЛЪБЃЌSUT е§дЕВњЩњКѓЛсШЁбљЕНHiЃЌвђДЫбЖКХEТэЩЯpull HiЁЃШєДЫЪБЮвУЧбЁдёremoveЮЊ/8ЪБЃЌШчЭМЪЎЖўCase3ЫљЪОЃЌENбЖКХЛсЮЌГж4*TSUTЕФЪБМфКѓзЊЮЊЕЭЕчЮЛЃЌвђДЫЕБSUTЯТвЛИіе§дЕВњЩњКѓЃЌЦфЛсШЁбљЕНLowЃЌДйЪЙбЖКХE pull downЁЃ

гЩЭМжаПЩвдПДГіЃЌбЖКХSUTОзЊЛЛКѓГЩЙІremoveЕє3.5ЃЈ=4-0.5ЃЉИіcyclesЃЌЧвSUTбЖКХжЛОЙ§вЛПХEDЁЃШчДЫвЛРДНЋПЩРГЄstable regionЃЌЮЌГжЗХДѓБЖТЪЃЌВЂвВВЛЛсвђЮЊШУД§ВтбЖКХТЗОЖЬЋГЄЖјИФБфдЯШжЎЖЖЖЏСПЁЃвђДЫРћгУЩЯЪіЫљЬсГіЖЖЖЏЗХДѓММЪѕДюХфТіВЈЭЬЪЩЙлФюжЎЕЅпЂШЁСПВтЗЈЃЌНЋПЩдкШЮКЮЦЕЖЮЯТЯпадЗХДѓД§ВтЪБТіЖЖЖЏЃЌвдРћКѓЖЮЪБМф-Ъ§ЮЛзЊЛЛЕчТЗжЎЖЖЖЏСПНтЮіЃЌВЂНтОіЦфвђжЦГЬЯожЦЫљдьГЩзМШЗЖШВЛзуЕФЮЪЬтЁЃ

ЪБМф-Ъ§ЮЛзЊЛЛЕчТЗЃЈTime-to-Digital ConverterЃЛTDCЃЉ

ЁЖЭМЪЎЫФ ЫљЬсГіжЎЪБМф-Ъ§ЮЛзЊЛЛЕчТЗЁЗ

дкБОЮФжаЮвУЧЬсГіаТЕФЪБМф-Ъ§ЮЛзЊЛЛЕчТЗЃЌетЪЧвђЮЊДЋЭГЪБМф-Ъ§ЮЛзЊЛЛЕчТЗЛљБОЩЯНдЪЧЪЙгУЖрМЖЛКГхЦїЛђЪЧбгГйЕЅдЊРДВњЩњЖрЯрЮЛбЖКХЃЌШЛКѓНхгЩШЁбљРДЕУЕНЪ§ЮЛТыЁЃШЛЖјвдФПЧА0.13-umЕФжЦГЬРДЫЕЃЌЦфЫљФмВњЩњЕФзюаЁЛКГхбгГйдМЮЊ25-psзѓгвЃЛврМДвдећИіЯЕЭГРДПДЃЌЦфФмВтЪдЕФзюИпНтЮіЖШвВЕШгк25-psЃЌДЫЙцИёдкЯжНёИпЫйгІгУжавбЮоЗЈТњзуВтЪдашЧѓЁЃ

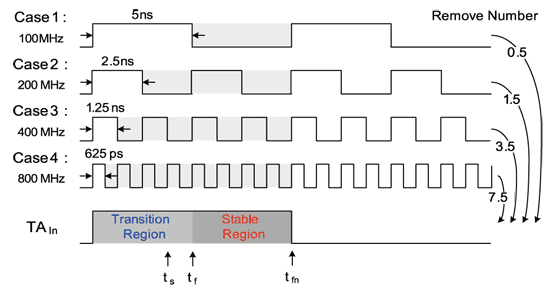

гаМјгкДЫЃЌЮвУЧНЋРћгУЖрЙЄЪНеёЕДЦїДюХфЯрЮЛФкВхЗЈЃЌРДЪЕЯжвЛНЯИпНтЮіЖШжЎЪБМф-Ъ§ЮЛзЊЛЛЕчТЗЁЃШчЭМЪЎЫФЫљЪОЁЃЦфжївЊАќКЌСЫвЛзщЖрЙЄЪНеёЕДЦїЃЈMuxed oscillatorЃЉЁЂЯрЮЛФкВхЕчТЗЃЈPhase InterpolatorЃЛPIЃЉвдМАШЁбљБрТыЕчТЗЃЌЕБжаЖрЙЄЪНеёЕДЦїЪЧгУРДВњЩњЖрЯрЮЛжЎВЮПМбЖКХЁЃЯрНЯДЋЭГЪЙгУopen loop delay chainЃЌclose loopвђгаЛиЪкЛњжЦЃЌЫљвдЛсОпгаНЯзМШЗЕФЕЅЮЛбгГйЪБМфЃЌЧвНЯВЛвзЪмЕНжЦГЬЦЏвЦжЎгАЯьЁЃСэЭтвђЮЊЪЧЪЙгУеёЕДдРэРДВњЩњЯрЮЛЃЌЫљвдПЩНхгЩВтЪдеёЕДЦЕЭЦЫуГіЕЅЮЛбгГйЪБМфЃЌНгзХШєдйДюХфЪЙгУФкВхЕчТЗММЪѕЃЌНЋПЩДѓЗљЬсЩ§ВтЪдНтЮіЖШЁЃ

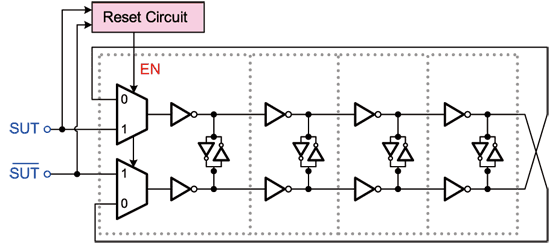

ЁЖЭМЪЎЮх ЖрЙЄЪНеёЕДЦїжЎЕчТЗМмЙЙЭМЁЗ

ЖрЙЄЪНеёЕДЦїЪЧЪБМф-Ъ§ЮЛзЊЛЛЕчТЗжазюЮЊживЊЕФЕчТЗЃЌвђЮЊЦфБиашвРД§ВтбЖКХЕФЩЯЩ§дЕЃЌРДеёЕДГігУРДБЛШЁбљжЎЖрЯрЮЛИпЫйбЖКХЁЃШчЭМЪЎЮхЫљЪОЃЌгЩСНИіЖрЙЄЦїЁЂЫФМЖбгГйЕЅдЊвдМАжижУЕчТЗЫљзщГЩЁЃЦфГЦЮЊЖрЙЄЪНеёЕДЦїЪЧвђЮЊДЫЕчТЗОпгаСНжжВйзїФЃЪНЃЌЗжБ№ЮЊеёЕДФЃЪНЃЈoscillating modeЃЉгыуХЫјФЃЪНЃЈlatching modeЃЉЃЌФЃЪНжЎЧаЛЛдђгЩжижУЕчТЗРДОіЖЈЁЃ

ЯрЙиВйзїдРэШчЯТЁЃЕБД§ВтбЖКХе§дЕВњЩњЪБЃЌжижУЕчТЗЛсЪфГіENЮЊЕЭЕчТЗЃЌДЫЪБЖрЙЄЦїбЁдёЕН0ЁЃвдЭМЪЎЮхЫљЪОЃЌДЫЪБЛиТЗПЩЪгЮЊвЛВюЖЏеёЕДЦїЃЌГжајЮШЖЈЬсЙЉЖрЯрЮЛжЎИпЫйВЮПМбЖКХЁЃШЛЖјЭЈГЃгкИїЯЕЭГжаЖЖЖЏСПНдВЛЛсГЌдНАыИіжмЦкЃЌвВОЭЪЧЃЈ1/2ЃЉxUIЃЌЫљвдЦфЪЕУПИіжмЦкФкЕФЖЖЖЏВтЪдНдЛсгкАыИіжмЦкФкНсЪјЃЌвђДЫжЛашгкД§ВтЕчТЗЕФАыИіжмЦкРяВњЩњГіД§ШЁбљбЖКХЁЃЛЛОфЛАЫЕОЭЪЧжЛашШУЖрЙЄЪНеёЕДЦїЙЄзїАыИіжмЦкКѓМДПЩЙиБеЁЃ

вђДЫЕБД§ВтбЖКХИКБпдЕвЛВњЩњЃЌжижУЕчТЗЛсЧПжЦENЮЊИпЕчЮЛЃЌДЫЪБЖрЙЄЦїНЋгЩ1ЕФТЗОЖЪфГіЃЌвВОЭЪЧЧаЛЛжСуХЫјФЃЪНЁЃгЩЭМжаПЩПДГіЃЌДЫЪБећЬхеёЕДЛиТЗвбБЛЧаЖЯЃЌЪфШыМДЮЊД§ВтбЖКХЃЌИїбгГйЕЅдЊЕФЪфГіВЛЪЧД§ВтбЖКХЕФбгГйЁЂОЭЪЧД§ВтбЖКХЕФЗДЯђбгГйЃЌжБжСе§БпдЕгжВњЩњКѓЃЌВХЛсЛжИДеёЕДФЃЪНвдРћЖЖЖЏжЎВтЪдЁЃ

ДЋЭГЪБМф-Ъ§ЮЛзЊЛЛЕчТЗЩшМЦЩЯЃЌЭЈГЃЛсЪмЕНжЦГЬЫљФмВњЩњЕФзюаЁеЂбгГйЫљЯоЖЈЁЃЮЊСЫПЫЗўДЫЮЪЬтЃЌЮвУЧВЩгУСЫГЃМћЕФЯрЮЛФкВхЕчТЗЃЌРДВњЩњаЁгквЛИібгГйЕЅдЊПЩЬсЙЉЕФбгГйЪБМфЁЃЯрЮЛФкВхЕчТЗЕФжБОѕЯыЗЈЪЧЯЃЭћФмЙЛдкСНИіЯрСкЯрЮЛЕФаХКХжЎМфВњЩњвЛИіаТЕФаХКХЃЌЖјЦфЯрЮЛЛсНщгкетСНЯрСкЯрЮЛаХКХМфЃЌНјЖјДяЕНЬсЙЉИќИпЯрЮЛНтЮіЖШЕФаХКХ [10]ЁЃ

аЁНс

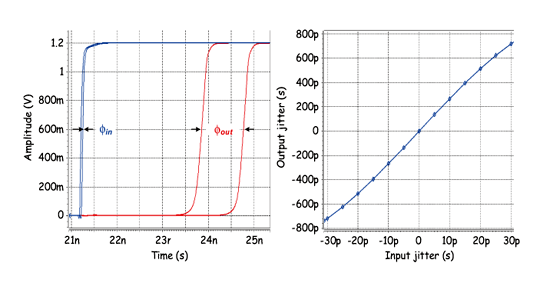

вдЩЯЮвУЧНщЩмФкНЈЖЖЖЏВтЪдЯыЗЈгыМмЙЙЃЌжївЊЪЧЯыНхгЩЗХДѓЪфШыЖЖЖЏСПРДНтОіДЋЭГВтЪдЗЈЮоЗЈВтЪдЕЭЖЖЖЏСПЕФЮЪЬтЃЌВЂДюХфЩЯЖрЙЄЪНеёЕДжЎЪБМф-Ъ§ЮЛзЊЛЛЕчТЗЃЌРДЬсЩ§ећЬхЯЕЭГНтЮіЖШЁЃДЫЭтвВвРЕчТЗВйзїЬиадЬсГівЛТіВЈЭЬЪЩЕчТЗЃЌЪЙЕУДЫВтЪдЯЕЭГНЋПЩгкИїЦЕЖЮНјааздЮвВтЪдЃЌНЋВЛЛсвђВйзїЫйЖШЖјгАЯьВтЪдЦЗжЪЁЃНгзХЯТвЛеТНкжаЃЌЮвУЧНЋРћгУHSpiceРДбщжЄЫљЬсГіжЎЗНЗЈгыМмЙЙЁЃ

ФЃФтНсЙћ

ЁЖЭМЪЎСљ ЖЏЗХДѓЕчТЗжЎзЊвЦЧњЯпЭМЁЗ

ЃЈXжсЃКЪфШыЖЖЖЏСПЃЛYжсЃКЪфГіЖЖЖЏСПЃЉ

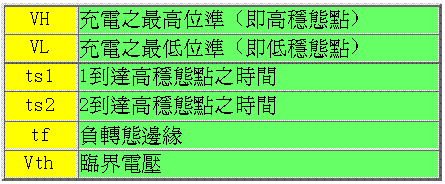

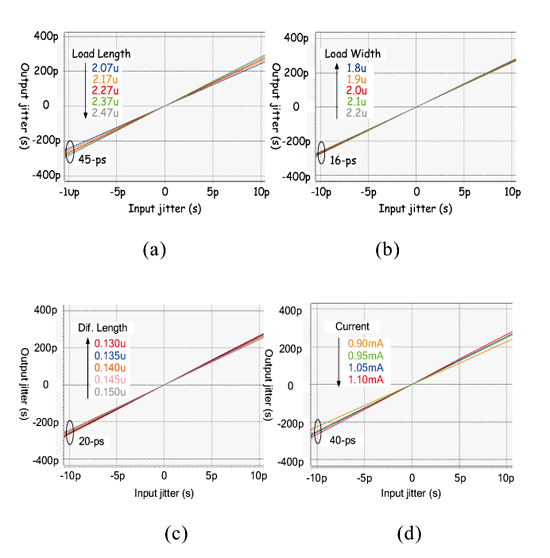

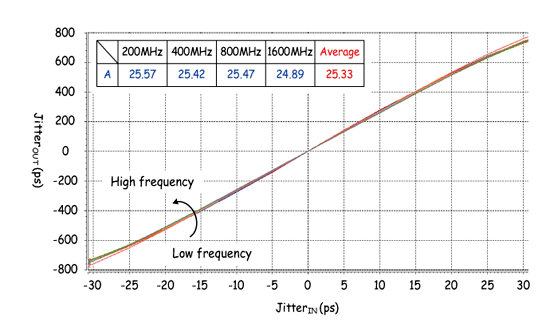

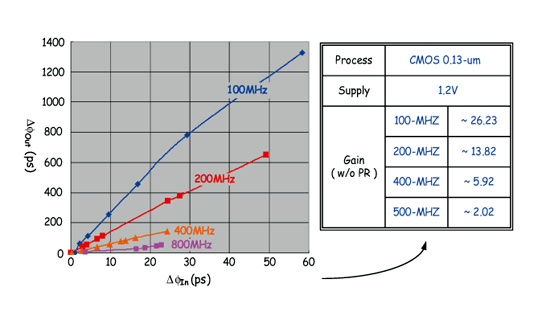

ФкНЈЖЖЖЏВтЪдМмЙЙжазюживЊЕФдЊМўЮЊЖЖЖЏЗХДѓЕчТЗЃЌвђЮЊЦфЗХДѓБЖТЪНЋгАЯьЯЕЭГНтЮіЖШвдМАЮШЖЈЖШЃЌЫљвдЪзвЊЙЄзїОЭЪЧШЗБЃЖЖЖЏЗХДѓЕчТЗВйзїЬиадЁЃШчЭМЪЎСљМДЮЊЖЖЖЏЗХДѓЕчТЗжЎФЃФтНсЙћЁЃЕБЪБТіЖЖЖЏВњЩњЪБЃЌОгЩДЫЕчТЗПЩАбЪБТіБпдЕГЖПЊЃЌвВОЭЪЧдіМгЯрЮЛЮѓВюСПЁЃСэЭтЮвУЧПЩРћгУВЛЭЌЪфШыЖЖЖЏСПРДЙлВтЖЖЖЏЗХДѓЕчТЗжЎВйзїЯпадЖШЃЌШчЭМЪЎЦпЫљЪОЁЃШєЫљФЃФтГіРДЕФзЊвЦЧњЯпГЪЯжЯрЭЌаБТЪЃЌДњБэДЫЕчТЗЕФЗХДѓБЖТЪЮЊвЛЖЈжЕЃЛЕЋШєЧњЯпГЪЯжГіаэЖраБТЪЃЌдђПЩУїЯдЙлВьГіЗХДѓБЖТЪгкВЛЭЌЪфШыЖЖЖЏЪБОпгаВЛЭЌЕФЗХДѓБЖТЪЃЌЫљвдЮвУЧБуашеыЖджЦГЬЦЏвЦЖдЕчТЗгАЯьзїФЃФтЗжЮіЁЃ

ЁЖЭМЪЎЦп ЗХДѓБЖТЪvs.жЦГЬЦЏвЦЃКЃЈaЃЉLoad lengthЃЛЃЈbЃЉLoad widthЃЛЃЈcЃЉDiff. pair lengthЃЛЃЈdЃЉBias currentЁЗ

ЁЖЭМЪЎАЫ ЗХДѓБЖТЪ vs. ВйзїЦЕТЪЁЗ

ЖЖЖЏЗХДѓЕчТЗЗжЮіНсЙћ

ЯШЧАНщЩмЙ§ЖЖЖЏЗХДѓЕчТЗЪЧНхгЩЕчСїГфЗХЕчЫйЖШРДДяЕНЖЖЖЏЗХДѓЃЌвђДЫИКдивдМАЕчШнСПНЋОіЖЈЖЖЖЏЗХДѓЕФГЬЖШЃЌЫљвдвдЯТОЭеыЖдЫФИіЙиМќЕузїЗжЮіЃЌВЂФЃФтЦфзЊвЦЧњЯпЭМЁЃгЩЭМЪЎЦпЫљЪОЃЌЃЈaЃЉЁЋЃЈdЃЉЗжБ№ЮЊИКдиЕчОЇЬхжЎlengthЁЂИКдиЕчОЇЬхжЎwidthЁЂВюЖЏЖдЕчОЇЬхжЎlengthКЭЦЋбЙЕчСїБфвьЪБжЎФЃФтЁЃДгжаПЩвдЙлВьГіЗХДѓБЖМИКѕНдЮЌГждкЙЬЖЈЕФБЖТЪЃЌЕЋдкИКдиЕчШнЃЈlengthЃЉгыВйзїЕчСїБфЛЏЪБЖдгкЯЕЭГгаНЯДѓЕФЦЋвЦСПЃЌдМ40-psЁЃ

ВЛЙ§вдећЬхЯЕЭГРДПДЃЌвђЮЊВЩгУЕФЪЧЗХДѓЖЖЖЏСПРДВтЪдЃЌдйНЋНсЙћГ§вдБЖТЪЕУЕНдЪМЖЖЖЏСПЃЌЫљвдЫфШЛФЃФтПДГіЗХДѓКѓЕФЖЖЖЏдМга40-psЕФБфвьЃЌЕЋГ§вдЗХДѓБЖТЪ25вдКѓЦфБфвьдМЮЊ1.6-psЃЌДЫЮѓВюСПЖдгкећЬхВтЪджЕМИКѕПЩКіТдВЛМЦЁЃДЫЭтЃЌЭМЪЎАЫЮЊЖЖЖЏЗХДѓЕчТЗВйзїгкВЛЭЌЦЕЖЮЕФзЊвЦЧњЯпЭМЁЃДгжаПЩУїЯдЗЂЯжЃЌВЛТлЪЧдкЕЭЦЕЛђЪЧИпЦЕВйзїЪБЃЌЦфНдОпгаНќЫЦЕФtransfer curveЃЌЫљвдМДбщжЄДЫЖЖЖЏЗХДѓЕчТЗОпгаПэВйзїЗЖЮЇвдМАЯпадЖЖЖЏСПЗХДѓжЎЬиадЁЃвђДЫгЩвдЩЯФЃФтПЩжЊЃЌЮвУЧЫљЬсГіжЎЖЖЖЏЗХДѓМмЙЙНЋПЩдЫгУдкЖЖЖЏВтЪдЯЕЭГжаЁЃ

ЁЖЭМЪЎОХ ФЃФтбщжЄгУжЎЖЖЖЏВњЩњЪОвтЭМЁЗ

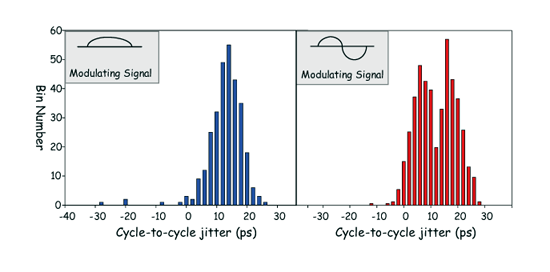

жмЦкЖджмЦкЖЖЖЏЯЕЭГЙлВь

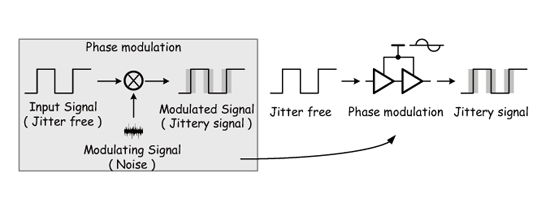

ЮЊСЫШЗБЃећЬхЯЕЭГВйзїе§ШЗадЃЌНгзХЮвУЧНЋЪЕМЪЪфШыжмЦкЖджмЦкЖЖЖЏжСЯЕЭГжаЃЌНхДЫЙлВьЦфВйзїЬиадЁЃЖјжмЦкЖджмЦкЖЖЖЏЕФВњЩњЗНЪНЃЌЮвУЧНЋВЩгУбЖКХЕїБфЗЈРДЪЕЯжЃЌШчЭМЪЎОХЫљЪОЁЃЦфАќКЌвЛИіИЩОЛЕФВЮПМЪБТіЃЈinput signalЃЉЁЂвЛИізїЮЊИЩШХдДЕФЕїБфбЖКХЃЈmodulating signalЃЉКЭЯрЮЛЕїБфЕчТЗЃЈphase modulatorЃЉЃЌНхгЩдгбЖШЅИФБфРэЯыЪБТізЊЬЌЕуЪЕЯжЖЖЖЏВњЩњЁЃ

ЖјвдЕчТЗУцРДПДЃЌЦфЪЕЯрЮЛЕїБфЕчТЗОЭЪЧПЩЕїећЕчдДЕчбЙЕФЖрМЖЛКГхЦїЁЃЕБвЛРэЯыЪБТіНјШыЛКГхЦїКѓЃЌЛсгабгГйВњЩњЃЌЖјбгГйСПКЭЕчдДЕчбЙгаМЋДѓЙиСЌадЁЃЕчбЙдНДѓбгГйдНаЁЃЛЗДжЎЕчбЙдНаЁбгГйОЭЛсдНДѓЁЃРћгУДЫЙиЯЕЃЌЮвУЧжЛвЊНЋЖЖЖЏзіЮЊЛКГхЦїЕчбЙЃЌОЭПЩвдЕУЕНЫцзХЖЖЖЏБфЛЏЕФЪБТіЯрЮЛЁЃ

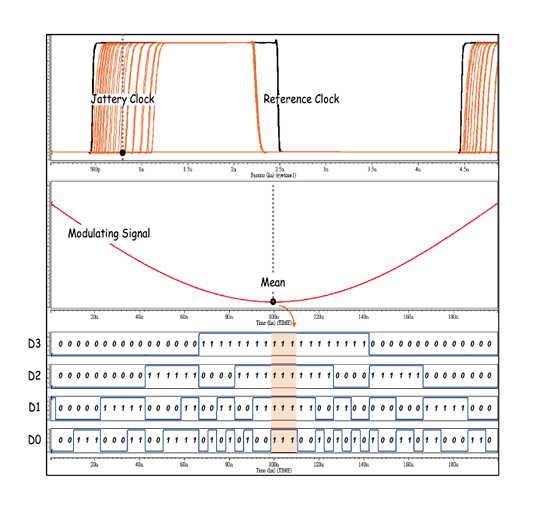

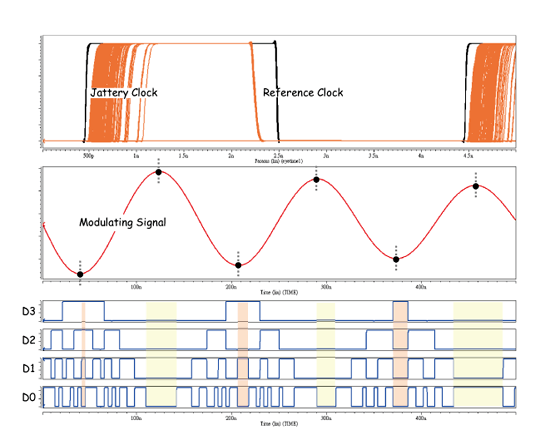

ЖЖЖЏЪ§ЮЛЛЏЙлВь

ЮЊСЫбщжЄДЫЯЕЭГЪЧЗёФме§ШЗЕиАбЪфШыЖЖЖЏЪ§ЮЛЛЏЃЌвђДЫЮвУЧвВНЋРћгУСНжжВЛЭЌаЭЬЌжЎЖЖЖЏРДбщжЄЃКвЛЮЊе§ЯвЖЖЖЏЁЂСэвЛЮЊеёЗљЕїБфЖЖЖЏЁЃШчЭМЖўЪЎКЭЖўЪЎвЛЫљЪОЕФЖЖЖЏСПЪ§ЮЛЛЏжЎФЃФтНсЙћЁЃДгжаПЩвдЕУжЊЃЌЯрЙиЯЕЭГПЩГЩЙІвРЪфШыЖЖЖЏаЭЬЌдЫЫуГіЖдгІЪ§ЮЛТыЃЌЮвУЧжЛашНЋЪ§ЮЛТыЖдееЖЖЖЏБэЃЌМДПЩЕУжЊЪфШыЖЖЖЏСПЁЃ

ЁЖЭМЖўЪЎ е§ЯвЖЖЖЏОЖЖЖЏВтЪдЯЕЭГжЎЪфГіНсЙћЁЗ

ЁЖЭМЖўЪЎвЛ ЕїЗљЖЖЖЏОЖЖЖЏВтЪдЯЕЭГжЎЪфГіНсЙћЁЗ

ЖЖЖЏВтЪдзМШЗЖШКЭВтЪдЪБМфЙиСЊУмЧаЃЌдкзуЙЛВтЪдбљБОЯТВХФмШЗБЃЫљЕУЪ§жЕОпБИЙЋаХСІЃЌдкВтЪдЪБОЭБиаыШУЯЕЭГзіГЄЪБМфРлМЦЁЃЮвУЧНЋВтЪдЧАЪіСНжжаЭЬЌжЎЖЖЖЏЗжВМЃЌДЫЪБЯЕЭГЛсЫЭГіаэЖрВтЪдЪ§жЕЃЛЖјЮЊСЫЕУжЊЦфецЪЕЖЖЖЏЗжВМЕФЧщПіЃЌвђДЫЮвУЧРлМгЫљгаЖЖЖЏСПЗжВМДЮЪ§ЃЌЦфВтЪдНсЙћШчЭМЖўЪЎЖўЫљЪОЁЃ

ЖЖЖЏЪ§жЕЖдгІЗжЮі

ОЙ§ГЄЪБМфдЫЫуКѓЃЌдкАыжмЦке§ЯвЖЖЖЏВПЗнЃЌЭМЖўЪЎЖўзѓУїЯдПЩПДГіЦфЮЊвЛИпЫЙЗжВМЃЌОпгавЛИіЗхжЕЃЌДЫжЕОЭТфгке§ЯвЖЖЖЏЕФзюДѓжЕЩЯЁЃЖјгвЭМеёЗљЕїБфЖЖЖЏжЎВтЪдНсЙћЃЌдђЯдЪОЫЋЗхжЎЖЖЖЏЗжВМЃЌЧвЦфЫЋЗхЕФЗжВМСПвВВЛОЁЯрЭЌЁЃетЪЧвђЮЊеёЗљЕїБфбЖКХУПИіЗхжЕЕчбЙВЛЭЌЃЌЖјВЛЭЌЕФЗхжЕЛсЖдгІЕНВЛЭЌЕФЪ§ЮЛТыЃЌЫљвддкГЄЪБМфЖЖЖЏВтЪдЯТВХЛсГіЯжДЫЗжВМЧщаЮЁЃ

НхгЩвдЩЯЕФЫЕУїПЩЕУжЊЃЌЮвУЧЫљЬсГіжЎЖЖЖЏВтЯЕЭГВЛЕЋПЩвдГЩЙІСПЛЏЖЖЖЏСПЃЌВЂПЩНхгЩГЄЪБМфЕФЗжЮіЃЌПЩНјвЛВНЕиЕУжЊЖЖЖЏЗжВМаЭЬЌЃЌИќПЩДгжадЫЫуГіЖЖЖЏЗхжЕЁЂЖЖЖЏОљЗНИљжВЁЂnБЖsigmaЕФЖЖЖЏЗжВМСП…ЕШЕШЁЃ

ЁЖЭМЖўЪЎЖў ГЄЪБМфРлМЦЖЖЖЏдЫЫуНсЙћЁЗ

ЫљЬсГіВтЪдЗЈжЎВтЪдНсЙћ

ЁЖЭМЖўЪЎШ§ ЖЖЖЏВњЩњЪОвтЭМгыЪЕМЪВтЪдЭМЁЗ

РћгУПэЦЕЖЖЖЏВтЪдбЖКХ

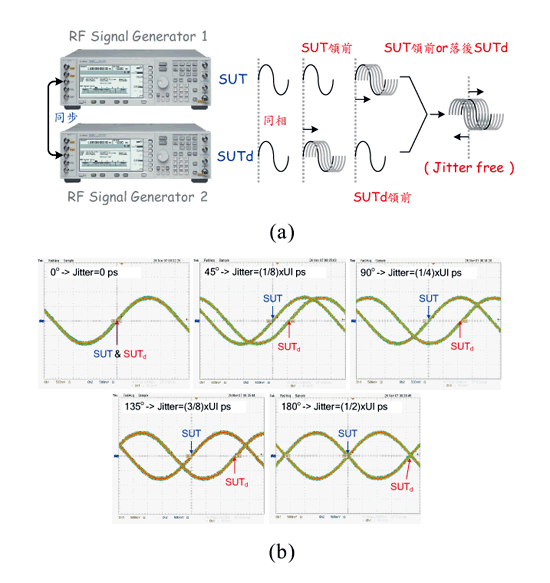

дкСПВтЛЗОГЕФНЈЙЙЩЯЃЌЮвУЧПЩЗжЮЊСНИіВПЗнЃКвЛЮЊеыЖдЖЖЖЏЗХДѓЕчТЗзїВтЪдЃЌСэвЛдђЮЊШЋЯЕЭГВтЪдЁЃдкЯШЧАМмЙЙЫЕУїжаЬсЕНЃЌЮвУЧЫљЬсГіЕФВтЪдМмЙЙЪЧеыЖдД§ВтбЖКХжЎжмЦкЖджмЦкЖЖЖЏзїВтЪдЃЌвђДЫашвЊвЛбгГйЕчТЗЃЌНЋУПИіжмЦкбЖКХгыбгГйвЛИіжмЦкЪБМфжЎбЖКХнЭШЁГіРДЁЃЕЋЮЊСЫвЊбщжЄЖЖЖЏЗХДѓЕчТЗВйзїЬиадЃЌЮвУЧвВашвЊвЛЗЧГЃПэЦЕгыПэЗЖЮЇЖЖЖЏВтЪдбЖКХЃЌвђДЫВЩгУЭМЖўЪЎШ§ЕФВтЪдЗЈЁЃ

врМДЮвУЧРћгУСНЬЈИпЦЕбЖКХВњЩњЦїЃЌЗжБ№ВњЩњДњБэSUTгыSUTdжЎД§ВтЪБТібЖКХЃЌвђЮЊЪБТівбЧПжЦЭЌВНЃЌЫљвдШєВЛИФБфШЮКЮВЮЪ§ЪБЃЌSUTгыSUTdжЎбЖКХНЋБЃГжЭЌЯрЮЛЁЃЖјЮЊСЫВтЪдЖЖЖЏЗХДѓЕчТЗЕФЗХДѓЬиадЃЌПЩНхгЩЕїећЦфжавЛЬЈбЖКХВњЩњЦїжЎбгГйСПЃЌРДЗТдьЪЕМЪЪБТіЖЖЖЏЧщаЮЁЃ

ШчЭМжаПЩвдЙлВьГіЃЌШєЕїећбЖКХВњЩњЦї2ЕФбгГйСПЃЌПЩЪЕЯжТфКѓЖЖЖЏЗжСПЃЛШєЕїећбЖКХВњЩњЦї1ЕФбгГйСПЃЌдђПЩЪЕЯжСьЧАЖЖЖЏЗжСПЃЌНхДЫЕїећНЋПЩДяЕНПэЖЖЖЏЗЖЮЇжЎВтЪдЁЃДЫЭтвђбЖКХВњЩњЦїПЩВњЩњДѓЗЖЮЇЦЕТЪЕїећЃЌЫљвдвВПЩНјвЛВНВтЪдЖЖЖЏЗХДѓЦїЯпадЖШЁЃ

ЁЖЭМЖўЪЎЫФ ЖЖЖЏЗХДѓЕчТЗСПВтЛЗОГЪОвтЭМЁЗ

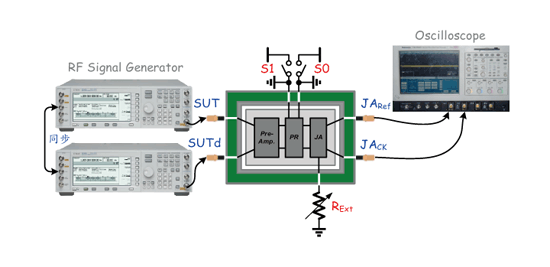

ЗжЮіВтЪдЙ§ГЬ

ЭМЖўЪЎЫФЮЊЖЖЖЏЗХДѓЕчТЗВтЪдЛЗОГЪОвтЭМЃЌЦфЪфШыбЖКХЮЊЧАЪіСНЬЈбЖКХВњЩњЦїЫљЬсЙЉжЎбЖКХЁЃгкОЇЦЌжаЧАЖЫЛсЯШгадЄЯШЗХДѓЦїЃЈpre-amplifierЃЉНЋЪфШызЊЛЛЮЊЗНВЈЃЌЫцжЎЫЭШыТіВЈЭЬЪЩЕчТЗгыЖЖЖЏЗХДѓЕчТЗжаЁЃЕБЖЖЖЏСПОЕчТЗЗХДѓКѓЃЌЮвУЧРћгУЪОВЈЦїРДЙлВтЪфГібЖКХМфЕФЯрЮЛВюЃЌдйНЋЪфГіЯрЮЛВюЃЈJACK-JARefЃЉГ§вдЪфШыЯрЮЛВюЃЈSUT-SUTdЃЉЃЌМДПЩЕУЕНЖЖЖЏЗХДѓЕчТЗжЎЗХДѓБЖТЪЁЃ

ДЫЭтЕБЪфШыбЖКХЦЕТЪИФБфЪБЃЌПЩНхгЩЕїећS1КЭS0РДбЁдёНЯЮЊЪЪЕБЕФТіВЈЭЬЪЩЪ§ЃЛЖјШєЕБЖЖЖЏЗХДѓЕчТЗгкжЦзїЪБЗЂЩњЦЏвЦЃЌдђПЩНхгЩЕїећЭтВПЕчзшRExtНјЖјИФБфЕчСїСПЃЌвдШЗБЃЖЖЖЏЗХДѓСПЕФзМШЗадЁЃвђДЫгЩвдЩЯЫљЪіжЎЗНЗЈЃЌНЋПЩВтЪдГіЖЖЖЏЗХДѓБЖТЪжЎЯпадЖШЃЈJitterIn vs. JitterOutЃЉЁЂВйзїЦЕПэЃЈЦЕТЪ vs. ЗХДѓБЖТЪЃЉгыЗХДѓБЖТЪКЭТіВЈЭЬЪЩЪ§МфЕФЙиЯЕЁЃ

ЁЖЭМЖўЪЎЮх ЖЖЖЏСПВтЯЕЭГжЎСПВтЛЗОГЪОвтЭМЁЗ

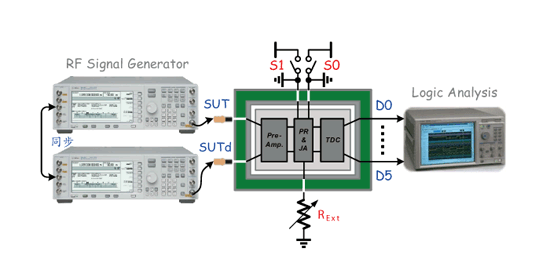

ЖЖЖЏСПВтЛЗОГЗжЮіЙ§ГЬ

СэЭтЭМЖўЪЎЮхЮЊЖЖЖЏСПВтЪдЯЕЭГжЎСПВтЛЗОГЪОвтЭМЁЃЦфЧАЖЫКЭЭМЖўЪЎЫФзіЗЈвЛжТЃЌЕЋвђЖЖЖЏЗХДѓЕчТЗКѓНгЩЯЪБМф-Ъ§ЮЛзЊЛЛЕчТЗЃЌвђДЫвбНЋЖЖЖЏСПЛЏГЩЪ§ЮЛТыЃЌЫљвдЮвУЧНхгЩТпМЗжЮівЧЃЈLogic AnalysisЃЛLAЃЉРДдЫЫуМДЪБЪфГіжЎЪ§ЮЛТыЃЛОвЛЖЮгааЇЪБМфдЫЫуКѓЃЌдйАбТпМЗжЮівЧЫљЪфГіжЎНсЙћгыЪфШыЖЖЖЏСПЯрБШНЯЃЌМДПЩЕУжЊЫљЬсГіжЎЯЕЭГзМШЗЖШЁЃ

ЁЖЭМЖўЪЎСљ ЪфШыЖЖЖЏгыЪфГіЖЖЖЏжЎСПВтЭМЃКЫцзХМ§ЭЗЗНЯђДњБэЪфШыЖЖЖЏЕндіЁЗ

ЪзЯШЃЌЮвУЧНЋЫљЬсГіЕФЖЖЖЏЗХДѓЕчТЗЃЌЪЙЦфВйзїдкВЛЭЌЪфШыЖЖЖЏСПЯТЃЌЙлВьЗХДѓБЖТЪМфЕФБфЛЏЃЌШчЭМЖўЪЎСљЫљЪОЁЃЮЊСЫВтЪдМЭТМЗНБуЃЌЮвУЧВЩгУ6ИіВтЪдpatternРДбщжЄЃЌвВОЭЪЧЫЕРћгУ6ИіВЛЭЌЕФЪфШыЖЖЖЏСПЫЭШыЖЖЖЏЗХДѓЕчТЗжаЃЌШЛКѓСПВтЪфГіЖЖЖЏСПЃЌвдЛцГіЖЖЖЏЗХДѓЧњЯпЭМЁЃДЫЭтЮЊСЫбщжЄЮвУЧЫљЬсГіЕФТіВЈЭЬЪЩЙлФюПЩаое§ЗХДѓЯпадЖШЃЌЫљвдвВеыЖдЫФИіЦЕЖЮзібщжЄЁЃ

ЁЖЭМЖўЪЎЦп ЖЖЖЏЗХДѓБЖТЪvs.ВйзїЦЕТЪЁЗ

ЖЖЖЏЗХДѓЕчТЗВтЪдНсЙћ

ЭМЖўЪЎЦпМДЮЊЖЖЖЏЗХДѓЕчТЗВтЪдНсЙћЁЃДгЭМжаПЩЙлВьГіЃЌдкЕЭЦЕВйзїЪБЃЌвђЮЊЮШЬЌЧјгђзуЙЛЃЌЫљвдЦфЪфГіЖЖЖЏгыЪфШыЖЖЖЏБШЃЌгыЕБГѕЫљЩшМЦЕФЯрОрВЛдЖЁЃЕЋЫцзХД§ВтбЖКХЦЕТЪЩЯЩ§ЁЂЮШЬЌЧјМфЫѕаЁЃЌдкВЛЕїећТіВЈЭЬЪЩЪ§ФПЕФЬѕМўЯТЃЌЗХДѓБЖТЪЛсЫцжЎЫѕаЁЃЌЩѕжСЗХДѓБЖТЪЯћЪЇЃЌЕМжТЯЕЭГВйзїДэЮѓЁЃвд800-MHzЕФЬѕМўЮЊР§ЃЌДЫЧјЖЮЗХДѓБЖТЪвбЯТНЕжСдМ2БЖзѓгвЃЌДЫЪБвбЭъШЋЮоЗЈУжВЙЪБМф-Ъ§ЮЛзЊЛЛЕчТЗНтЮіЖШВЛзуЕФШБЕуЁЃвђДЫДгДЫВтЪдПЩЙлВьГіЃЌЫфгкИїЦЕЖЮФкЗХДѓБЖТЪНдПЩЮЌГжЗХДѓБЖЙЬЖЈЃЌЕЋжЛвЊЪфШыбЖКХЦЕТЪвЛБфЛЏЃЌОЭЛсдьГЩЗХДѓБЖТЪЪЇецвджСгкЛсгаЮѓХаЕФЧщаЮЁЃвђДЫНгЯТРДНЋвРЧАЪіЕФЫЕУїЪЪЕБЧаЛЛТіВЈЭЬЪЩЪ§ЃЌРДДяЕНПэЦЕжЎЗХДѓБЖТЪЁЃ

ШчЭМЖўЪЎАЫЫљЪОЃЌдкВЛЭЌЦЕЖЮВйзїЯТЮвУЧШЅИФБфТіВЈЭЬЪЩЕФЪ§ФПЃЌвВОЭЪЧЧаЛЛS0ЁЂS1ЃЌШУЖЖЖЏЗХДѓЕчТЗдкВЛЭЌЦЕЖЮЯТНдОпгазуЙЛПэЕФЮШЬЌЧјМфЁЃДЫЭтвВНхгЩЕїећЭтЕїЕчзшНЋЖЖЖЏЕчТЗжЎЗХДѓБЖТЪзїаЉЮЂЕФаое§ЁЃЭМжаЯдЪООЕїећТіВЈЭЬЪЩЪ§КѓЃЌгкЪ§ЪЎMHzЁЋ1.6GHzИННќЦфЗХДѓБЖМИКѕЮЌГждк25.5БЖзѓгвЁЃЕЋШєГЌЙ§1.6GHzКѓЃЌвђЮЊtfnЪБМфЕуТ§Т§ППНќtsдьГЩЮШЬЌЕчЮЛЕФБфЛЏЃЌЫљвдЗХДѓБЖТЪПЊЪМгааЉаэИФБфЁЃВйзїЦЕТЪМЬајЭљЩЯЩ§ЃЌtfnЕуЛсЕШгкЛђЪЧГЌЧАtsЃЌдьГЩЗХДѓБЖТЪМБЫйЯТНЕЃЌЫљвдЫЕДЫЖЖЖЏЗХДѓЕчТЗЕФЯпадЗХДѓЧјЮЊЪ§ЪЎMHz~1.6GHzЁЃдкДЫБиаыЫЕУївђЮЊЯпадЧјМфПЩНхгЩИФБфТіВЈЭЬЪЩЕФЪ§ФПРДДяГЩЃЌвђДЫШєаыВйзїдкИќИпЦЕЕФдЫгУЩЯЪБЃЌЮвУЧжЛашвРдьЃЈ2ЃЉЪНРДЪЕЯжМДПЩЁЃ

ЁЖЭМЖўЪЎАЫ ЗХДѓБЖТЪгыЦЕТЪМфжЎЙиЯЕЭМЁЗ

ЁЖЭМЖўЪЎОХ ЖрЙЄЪНеёЕДЦїжЎеёЕДЦЕТЪВтЪдЭМЁЗ

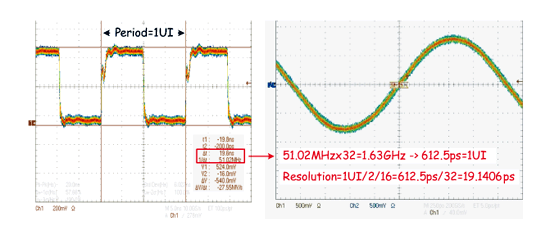

ЪБМф-Ъ§ЮЛЕчТЗзюМбНтЮіЖШ

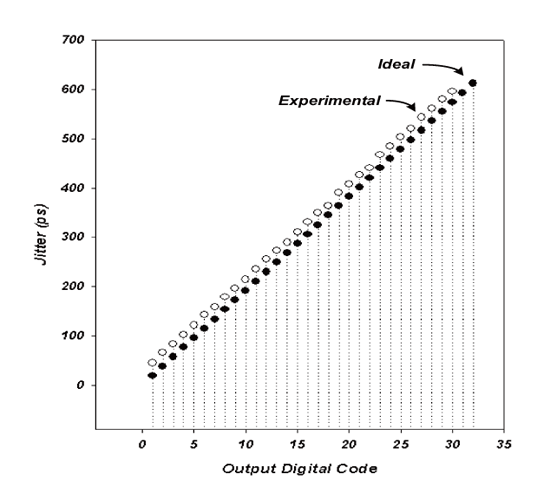

Г§СЫЖЖЖЏЗХДѓЕчТЗВтЪдЭтЃЌЪБМф-Ъ§ЮЛзЊЛЛЕчТЗвВЙиЯЕЕНЯЕЭГзюМбНтЮіЖШЁЃвђДЫвВНхгЩЕїећЪфШыЖЖЖЏСПРДЙлВьЪ§ЮЛЪфГіТыЃЌВЂВтЪдЖрЙЄЪНеёЕДЦїеёЕДЦЕТЪРДЛиЭЦНтЮіЖШЁЃШчЭМЖўЪЎОХЫљЪОЃЌЮЊСЫВтЪдЗНБуЃЌЮвУЧНЋеёЕДЦЕТЪГ§вд32РДЙлВтЃЌЫљвдДЫЪБМф-Ъ§ЮЛзЊЛЛЕчТЗЕФзюМбНтЮіЖШЃЌЮЊеёЕДжмЦкГ§ЩЯ32ИіЯрЮЛЃЈОФкВхКѓЫљЕУЃЉЃЌврМДдМЮЊ19-psЁЃ

ДЫЭтЭМШ§ЪЎЮЊЪфШыЖЖЖЏСПгыЪ§ЮЛЪфГіТыжЎЖдееЭМЁЃЦфЯдЪОЪфШыЖЖЖЏУПдіМг19-psЪ§ЮЛТывВЫцжЎдіМгЃЌЕЋСПВтЧњЯпгыРэЯыЧњЯпМфЯрВюдМ40-psЁЃДЫЮѓВюСПРДздгкеёЕДЦїжЎЖЖЖЏЁЃЕЋвдЯЕЭГВуУцРДПДЃЌЮвУЧжЛвЊНЋДЫЮѓВюСППлГ§МДПЩЃЌвђЮЊЦфЫљЙиаФЕФЪЧУПИіЪ§ЮЛТыМфЫљДњБэЕФЖЖЖЏСПЪЧЗёЯрЭЌЃЌвђДЫЮвУЧНЋЭМШ§ЪЎЮѓВюСПЙщСуКѓНјааЛ§ЗжЗЧЯпадЮѓВюСПЃЈIntegral NonlinearityЃЛINLЃЉжЎЗжЮіЃЌШчЭМШ§ЪЎвЛЫљЪОЁЃДЫЪБМф-Ъ§ЮЛзЊЛЛЕчТЗзюДѓЦЋвЦСПдМЮЊ6-psЃЌМД0.32LSBЃЈ1LSB=19-psЃЉЃЌЦфаЁгк0.5LSBЃЌЫљвдПЩЫЕЖдгкЯЕЭГВйзїЪБВЂВЛЛсДјРДбЯжиЕФДэЮѓЁЃ

ЁЖЭМШ§ЪЎ ЪфШыЖЖЖЏ vs. Ъ§ЮЛЪфГіТыЁЗ

ЁЖЭМШ§ЪЎвЛ ЪБМфЪ§ЮЛзЊЛЛЦїжЎINLЗжЮіЭМЁЗ

ЕУГіЯЕЭГНтЮіЖШ

ШЗЖЈСЫЖЖЖЏЗХДѓЕчТЗгыЪБМф-Ъ§ЮЛзЊЛЛЕчТЗВйзїЬиадКѓЃЌНгзХЮвУЧНЋПЩЭЦЕУЯЕЭГНтЮіЖШЁЃвђЮЊЗХДѓБЖТЪAгыбгГйЕЅдЊжЎбгГйЪБМфЕФБШР§ЮЊ25.5:19ЃЌЫљвддкДЫЬѕМўЯТЫљФмВтЕНЕФзюМбНтЮіЖШМДЮЊ19-ps/25.5=0.8-psЁЃЭЌРэПЩжЄЃЌШєдкЩшМЦЩЯНЋБЖТЪЬсЩ§ЛђЪЧЫѕаЁбгГйЪБМфжСЦфБШР§ЮЊ1:2ЪБЃЌДЫНЋПЩАбНтЮіЖШНјвЛВНЬсЩ§жС0.5-psЁЃгаМјвдЩЯСПВтгыФЃФтжЎНсЙћЃЌЮвУЧПЩвдЫЕДЫВтЪдЗНЗЈНЋПЩГЩЙІдЫгУдкwide rangeвдМАlow jitterЕФФкНЈЪБТіЖЖЖЏВтЪдМмЙЙжаЁЃ

Нсгя

дкЯШЧАЫљСаОйЕФЮхжжДЋЭГВтЪдМмЙЙЃЌВЛЭтКѕЪЧРћгУЕчТЗММЧЩРДЫѕаЁбгГйЕЅдЊЕФбгГйЪБМфЃЌвдЕШаЇдіМгВтЪдНтЮіЖШЁЃШЛЖјЕБВтЪдЫйЖШЩЯЩ§ЛђЪЧЖЖЖЏСПРДЕНsub-psЕШМЖКѓЃЌвђЕчТЗгыжЦГЬЩЯжЎЦПОБЃЌЦфЫљФмСПВтЕФЗЖЮЇНдЛсЪмЕНЯожЦЁЃ

ЛљгкЩЯЪіжЎдвђЃЌБОЮФЬсГіВЛЭЌгкДЋЭГВтЪдМмЙЙЕФВтЪдВпТдЁЃетЪЧВЩгУЖЖЖЏЗХДѓЕФЙлФюЃЌЯШеыЖдД§ВтбЖКХЖЖЖЏСПзіЯШЦкЗХДѓЃЌШЛКѓРћгУЪБМф-Ъ§ЮЛзЊЛЛЕчТЗНЋЖЖЖЏСПЛЏЃЌдйАбЕУЕНЕФЪфГіЪ§ЮЛТыГ§вдЗХДѓБЖТЪЃЌМДПЩЛЙдГідБОЕФжмЦкЖджмЦкЖЖЖЏСПЁЃДЫЭтЮЊСЫШУДЫВтЪдМмЙЙФмВйзїдкШЮКЮЦЕЖЮЯТЃЌвђДЫЛЙВЩгУЕЅпЂШЁДюХфТіВЈЭЬЪЩЕФВтЪдЗНЗЈЃЌРГЄЖЖЖЏЗХДѓЪБЕФЮШЬЌЪБМфЃЌвдЕУЕНЙЬЖЈЗХДѓБЖТЪЃЌНјЖјМѕЩйвђЦЕТЪБфЛЏЫљДјРДЕФСПВтЮѓВюЁЃЫљвдБОЮФЫљЬсГіЗНЗЈЯрНЯгкДЋЭГВтЪдЗНЪНЃЌНЋОпБИПэЦЕВйзїЁЂЕЭЖЖЖЏСПВтЪдЁЂИпНтЮіЖШЁЂГЩБОЕЭЁЂЪмВтЪдЛЗОГЯожЦГЬЖШаЁЕШгХЕуЁЃзюКѓЦфБШНЯШчБэШ§ЫљЪОЁЃ

(БэШ§) ИїжжМмЙЙБШНЯБэ

ЃЈЭъЃЉ

ЃЈзЊздЙЄбадКЯЕЭГОЇЦЌПЦММжааФММЪѕЦкПЏЕк8ЦкЁЃзїепРюшЄКЭжЃФЫЖGЃЉ